The RISC-V movement has taken off so quickly because of the wide range of choices it offers designers. However, massive flexibility creates its own challenges. One is how to analyze, optimize, and verify an unproven RISC-V core design with potential microarchitecture changes allowed within the bounds of the specification. … Read More

Author: Don Dingee

Systematic RISC-V architecture analysis and optimization

Points teams should consider about securing embedded systems

Wishful thinking once prevailed that embedded systems, especially small embedded devices, rarely needed security, and if they did, simply installing a “secure” operating system or a security chip would keep them safe. Connecting devices big and small on the Internet of Things (IoT) shattered such insular thinking… Read More

400 GbE SmartNIC IP sets up FPGA-based traffic management

Sustaining wire-speed 400 GbE transfers is only a first step in managing enterprise traffic. Adding rules-based filtering to sift packets in real time can stress most networking hardware to a breaking point, slowing down an entire network. Architects are trying to spread these loads, distributing intelligent traffic management… Read More

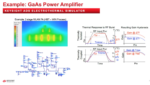

Transforming RF design with curated EDA experiences

Access to sophisticated RF EDA tools is one thing. Effectively harnessing their capability in real-world use is another. Digital EDA and test & measurement providers have long recognized ongoing customer education needs for their solutions. Keysight is embarking on an initiative to develop curated EDA experiences with… Read More

Crypto modernization timeline starting to take shape

Post-quantum cryptography (PQC) might be a lower priority for many organizations, with the specter of quantum-based cracking seemingly far off. Government agencies are fully sensitized to the cracking risks and the investments needed to mitigate them and are busy laying 10-year plans for migration to quantum-safe encryption.… Read More

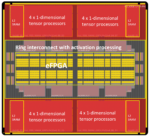

Reconfigurable DSP and AI IP arrives in next-gen InferX

DSP and AI are generally considered separate disciplines with different application solutions. In their early stages (before programmable processors), DSP implementations were discrete, built around a digital multiplier-accumulator (MAC). AI inference implementations also build on a MAC as their primitive. If the interconnect… Read More

Formal-based RISC-V processor verification gets deeper than simulation

The flexibility of RISC-V processor IP allows much freedom to meet specific requirements – but it also opens the potential for many bugs created during the design process. Advanced processor features are especially prone to errors, increasing the difficulty and time needed for thorough verification. Born out of necessity, … Read More

Configurable RISC-V core sidesteps cache misses with 128 fetches

Modern CPU performance hinges on keeping a processor’s pipeline fed so it executes operations on every tick of the clock, typically using abundant multi-level caching. However, a crop of cache-busting applications is looming, like AI and high-performance computing (HPC) applications running on big data sets. Semidynamics… Read More

Advanced electro-thermal simulation sees deeper inside chips

Heat and semiconductor reliability exist in an inversely proportional relationship. Before the breaking point at the thermal junction temperature rating, every 10°C rise in steady-state temperature cuts predicted MOSFET life in half. Yet, heat densities rise as devices plunge into harsher environments like smartphones,… Read More

eFPGA goes back to basics for low-power programmable logic

When you think “FPGA,” what comes to mind? Massive, expensive parts capable of holding a lot of logic but also consuming a lot of power. Reconfigurable platforms that can swallow RTL for an SoC design in pre-silicon testing. Big splashy corporate acquisitions where investors made tons of money. Exotic 3D packaging and advanced… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era