When Apple announced last September their A7 chip had gone 64-bit, the congregation immediately swooned, but analysts reacted skeptically: “So what? Phones don’t need more memory, and there are no 64-bit apps.” Even pundits miss once in a while, and now the topic is how the chip industry is headed for 64-bit.… Read More

Author: Don Dingee

Curved touchscreens

CES 2014 was the modern technology equivalent of the voyage of Ferdinand Magellan, proving beyond any shadow of doubt displays no longer can be thought of as only flat. While the massive curved 105-inch TVs shown by LG and Samsung drew many gawkers, the implications of curved touch displays are even wider.… Read More

Somebody at the NSA has a sense of humor

We have to go way back in the annals of entertainment history to find the origin of the word “Jeep”, not just a term of endearment hung on a WWII utility vehicle. Pictured is Eugene the Jeep, a mystical creature belonging to the 4th Dimension, who first appeared to torment Popeye the Sailor in 1936.… Read More

2014: Keep calm, and program gates

I was tempted to call this piece “if you’re not using an FPGA, you’re doing it wrong,” but that didn’t quite capture the whole picture. Social memes aside, the FPGA as we know it is undergoing a serious transformation into a full blown SoC, and 2014 is the year that will usher in one of the biggest changes in the history of embedded design.… Read More

Raised on radio: RPUs target autos and wearables

We’ve become familiar with Imagination Technologies as a leading provider of IP for mobile GPUs, and within the last year the acquisition of the MIPS architecture has established them further in NPU and SoC circles. Their latest move targets an IP solution more in line with their heritage.

Imagination, way before becoming famous… Read More

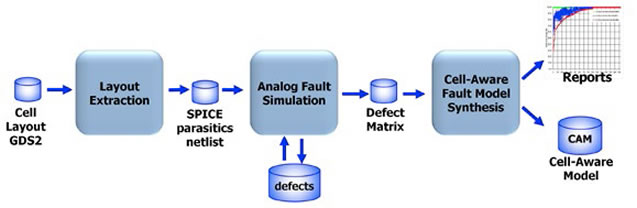

Patterns looking inside, not just between, logic cells

Traditional logic testing relies on blasting pattern after pattern at the inputs, trying to exercise combinations to shake faults out of logic and hopefully have them manifested at an observable pin, be it a test point or a final output stage. It’s a remarkably inefficient process with a lot of randomness and luck involved.

Getting… Read More

A little FPGA-based prototyping takes the eXpress

Ever sat around waiting for a time slot on the one piece of big, powerful, expensive engineering equipment everyone in the building wants to use? It’s frustrating for engineers, and a project manager’s nightmare: a tool that can deliver big results, and a lot of schedule juggling.… Read More

Conquering errors in the hierarchy of FPGA IP

FPGA design today involves not only millions of gates on the target device, but thousands of source files with RTL and constraints, often generated by multiple designers or third party IP providers. With modules organized in some logical way describing the design, designers brace themselves for synthesis and a possible avalanche… Read More

Because X doesn’t always mark the exact spot

Digital hardware has a habit of deciding – based on the bias and behavior of transistors – to drive outputs to a 0, or a 1, or if commanded a high-impedance Z state. SystemVerilog recognizes a fourth state: X, the “unknown” state a simulator has trouble inferring.

Simulators have a choice. Under X-optimism, they can convert the unknown… Read More

It’s about the mobile GPU memory bandwidth per watt, folks

There has been a lot of huffing and puffing lately about 64-bit cores making it into the Apple A7 and other mobile SoCs, and we could probably dedicate a post to that discussion. However, there are a couple other wrinkles to the Apple A7 that should be getting a lot more attention.

There are two primary causes of user frustration in multimedia… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era