4K UHD TVs were all dressed up at CES 2014 with no content to show. The good news for the 2014 holiday season is the industry has converged on one set of standards for display, interfacing, and encoding, so consumers should not be left marooned in an instant replay of the 3DTV hype-crash cycle. It may be a bit longer before everyone can… Read More

Author: Don Dingee

SIM cards and avoiding stranded IoT assets

Since pennants, drums, smoke, and horses fell out of favor to more advanced communication technology, network operators have struggled to find balance. Too few subscribers interested, and infrastructure investments completely fail. Just the right number of paying users, revenue streams provide profit and ability to invest… Read More

Using HAPS-DX for system-level deep trace debug

Debugging an ASIC design in an FPGA-based prototyping system can be a lot like disciplining a puppy. If you happen to be there at the exact moment the transgression occurs and understand what led up to that moment, administering an effective correction might be possible.

Catching RTL in the act requires the right tools. Faults in… Read More

Arteris on a winning streak in 2014

When Arteris sold key network-on-chip intellectual property and most of its human assets to Qualcomm earlier this year, it was big news. We suggested the bigger news after a restaffing effort would be a next-generation NoC release, and a new round of design wins.

Some developments were already in the pipeline. … Read More

Analyzing Cortex-A53 octa-core on Linux

Octa-core sells smartphones and tablets. 64-bit ARM Cortex-A53 implementations are available from Huawei, MediaTek, Qualcomm, Samsung, and now Marvell, with Rockchip and others on the way. Suddenly, almost everyone planning to run Linux is being asked for octa-core designs.

If it were easy, anyone could do it. Increasing … Read More

Money for data and your MEMS for free

An ongoing IoT debate centers on the notion that just because we can do something does not mean we should. From discussions at the recent MEMS Executive Congress, looking at what TSMC and some others see as the endgame for a trillion sensors signals possible trouble ahead.… Read More

MQTT not IoT “god protocol”, but getting closer

One protocol, and its descendants, drove the success of the World Wide Web. IP, or Internet Protocol, is the basis of every browser connection and the backbone of IT data centers. Some assumed that the Internet of Things would follow suit,… Read More

GNSS, dead reckoning, and MEMS IMUs

GNSS is a wonderful invention, and low cost receivers have crept into smartphones and other mobile devices. However, GNSS does not solve all problems, especially in urban environments. The canyon effect blocks signals at street level between tall buildings, and signals do not penetrate to the interior of parking garages, tunnels,… Read More

G.fast on the copper quick road for broadband

After a four year gestation period typical of global communications standards, G.fast has reached the point where chipset makers can implement parts against stable specifications. Formal approval of the physical layer spec, G.9701, is expected by the end of 2014. G.9700, dealing with power spectral density issues, was approved… Read More

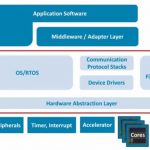

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era