Reconfigurable computing began with FPGA cards dropped into expansion slots in workstations. FPGA-based prototyping vendors tended away from that model as interconnect speeds rose and cabling complexity between modules increased. Much faster PCIe interfacing and bigger FPGAs mean revisiting the concept.… Read More

Author: Don Dingee

SoC power management a study in transition latency

Apple’s recent bout with ‘Batterygate’ highlighted just how important dynamic power management can be. Our last Sonics update looked at using their NoC to manage power islands; this time, we look at their research progress on architectural measures for power management.… Read More

New CEVA X baseband architecture takes on multi-RAT

What we think of as a “baseband processor” for cellular networks is often comprised of multiple cores. Anecdotes suggest to handle the different signal processing requirements for 2G, 3G, and 4G networks, some SoC designs use three different DSPs plus a control processor such as an ARM core. That’s nuts. What is the point of having… Read More

Reconfigurable redefined with embedded FPGA core IP

On November 1, 1985, before anyone had heard the phrase field programmable gate array, Xilinx introduced what they called a “new class of ASIC” – the XC2064, with a whopping 1200 gates. Reconfigurable computing was born and thrived around the RAM-based FPGA, whose logic and input/output pins could be architected into a variety… Read More

Fastest SoC time-to-success: emulators, or FPGA-based prototypes?

Hardware emulators and FPGA-based prototyping systems are descendants of the same ancestor. The Quickturn Systems Rapid Prototype Machine (RPM) introduced in May 1988 brought an array of Xilinx XC3090 FPGAs to emulate designs with hundreds of thousands of gates. From there, hardware emulators and FPGA-based prototyping … Read More

Low end LTE UE categories seeing more action

Most of our attention goes toward the higher end of the LTE UE categories – ones designed for moving large amounts of multimedia data from smartphones and tablets concurrently with voice traffic. An equally interesting discussion is taking shape at the low end of the LTE UE categories targeting M2M and IoT devices with power-efficient,… Read More

Updated tool cuts through DO-254 V&V chaos

Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

Steve Furber has found his million ARM cores

Some people say that everything in our lives happens for a reason. As we wrote Part I of “Mobile Unleashed”, the origin story of ARM architecture and its main progenitors Steve Furber and Sophie Wilson, we found what seemed like an obvious technological breakthrough was far from an overnight success – and it led to fascinating twists… Read More

Chips on the road to deep learning

CES has been morphing into an automotive show for several years now. Chipmakers were pitching control solutions, infotainment solutions, then connectivity solutions. Phone makers pitched device integration. Automotive electronics suppliers pitched MEMS sensors and cameras. Now, with a lot of pieces in place, the story … Read More

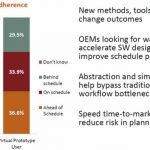

Maybe not the world, but schedules got eaten

It has been almost five years since Marc Andreessen wrote the words, “Software is eating the world.” The premise of his essay in the Wall Street Journal in 2011 was pretty simple: the technology world has seen its intrinsic value shift from hardware to software. New all-software names have appeared on the list of high flying companies,… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era