Our semiconductor industry uses many different materials and chemicals in the production of chips, boards and electronic systems. But what should we do if the minerals like tantalum, tin, tungsten and gold are coming from the eastern provinces of the Democratic Republic of the Congo where armed bandits are forcing workers against… Read More

Author: Daniel Payne

Hyperloop: Faster Than the Shinkansen

In 1987 I made my first trip to Japan for business, then rode in my first high-speed train on the fabled Shinkansen (aka bullet train) traveling up to 200 mph on the way from Tokyo to Kyoto. Compared to the USA, our engineering friends in Japan have the most futuristic high-speed trains in the world. Today there’ s talk about another… Read More

Is That My Car on Fire?

I was kind of shocked when the service manager at our local VW dealership told me that one of the wires in the ignition system of my wife’s New Beetle had started to overheat, melting the insulation and becoming a safety hazard. Why didn’t a fuze just blow, protecting the wiring from overheating? We decided to quickly … Read More

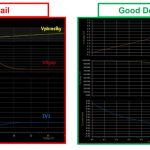

Design and Optimization of Analog IP is Possible

Designing Analog IP is often referred to as a “black art”, something that only highly experienced craftsmen can produce using transistor-level techniques that aren’t shared outside of their closely held group of trusted co-workers. I’d like to suggest that Analog IP can be designed and optimized … Read More

Academia and TCAD Grow Closer

On my first trip to Austria for EDA business I traveled by car from Germany, and I couldn’t wait to see how fast we would travel on the fabled Autobahn. Oddly enough it was summertime and the Autobahn was filled with vacationing families driving cars with shiny, aluminum campers in tow, so our car only traveled about 60 mph, nothing… Read More

An Easier Way to Reach Design Closure for SoC

It’s really challenging to reach design closure of an SoC by meeting timing constraints, staying within the power budget, tracking progress, communicating within the team, minimizing the floorplan, maximizing manufacturability and eliminating hotspots. Most SoC design teams have EDA tools from multiple vendors,… Read More

Smartphone Trends Revealed

I’ve been using cell phones since the 1980’s and I’ll never forget my first one, the Motorola DynaTAC (aka Brick Phone). The data plan was paid for by my EDA employer, and it did make me more productive because clients, prospects and co-workers could get a hold of me by simply dialing, not having to go through a secretary… Read More

Moore’s Law and Silicon Forest

When I first moved to Oregon in 1978 the largest industry was forestry, but then the endangered Spotted Owl was found and that put an end to many forestry companies and decimated the economy of many rural cities. Strangely enough it turns out that the Spotted Owl was found in great numbers across multiple states, so it never should’ve… Read More

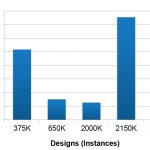

How Can Big Data and EDA Tools Help?

Big data is a headline phrase that I see appear almost weekly now in my newsfeed, so it’s probably time that I start paying more attention to the growing trend because it does impact how technology-driven, EDA tool flows are being used. From my last trip to DAC I recall only two companies that were really focused on system-level… Read More

Three New Things from ITC this year

The NFL has its annual Super Bowl contest each year, EDA vendors attend DAC, then the test folks attend ITCwhich was in Anaheim a few weeks ago. I’ve marketed ATGP, BIST and DFT tools before so I like to keep updated on what’s happening at conferences like ITC. Robert Ruiz from Synopsys spoke with me by phone to provide … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?