Earlier this month I attended a webinar organized by Methodics on the topic of IP life cycle management and traceability, with three presenters and a Q&A session at the end. I’ve worked with Michael Munsey before and he was the first presenter. Semiconductor IP creation and re-use is the foundation of all modern IC designs,… Read More

Author: Daniel Payne

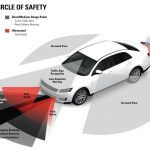

Meeting Automotive IC Design Challenges for Safety using On-Chip Sensors

I’ve been driving cars since 1978 and have even done a few DIY repairs in the garage, so I know how warm the engine compartment, transmission or exhaust system can become which makes automotive IC design rather unique in terms of the high temperature and voltage ranges that an electronic component is subjected to. Our safety… Read More

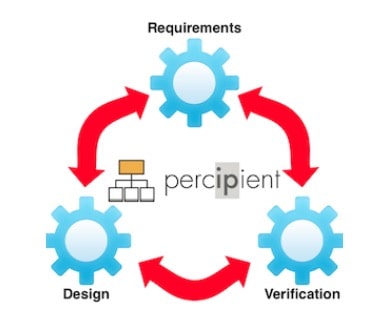

Webinar: ISO 26262 Compliance

To me the major idea of ISO 26262 compliance is ensuring that requirements can be traced throughout the entire design and verification process, including the use of IP blocks. The first market application that comes to mind with ISO 26262 is automotive, with its emphasis on safety because human lives are at stake. Since necessity… Read More

Deep Learning, Reshaping the Industry or Holding to the Status Quo

AI, Machine Learning, Deep Learning and neural networks are all hot industry topics in 2019, but you probably want to know if these concepts are changing how we actually design or verify an SoC. To answer that question what better place to get an answer than from a panel of industry experts who recently gathered at DVcon with moderator… Read More

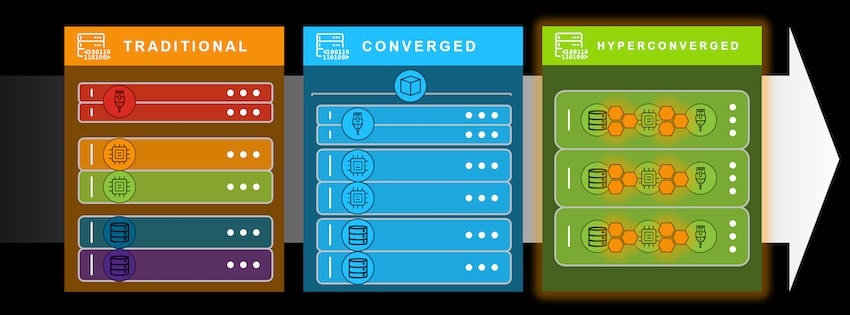

IC Implementation Improved by Hyperconvergence of Tools

Physical IC design is a time consuming and error prone process that begs for automation in the form of clever EDA tools that understand the inter-relationships between logic synthesis, IC layout, test and sign-off analysis. There’s even an annual conference called ISPD – International Symposium on Physical Design… Read More

DAC56 Keynotes and SKYtalks – The Big Picture

Many of us have engineering degrees and are well paid to maintain a deep but narrow focus into a specific domain, but what about the big picture, like industry trends and emerging challenges? Well, DAC56 has just the thing to deliver us a front row seat to the big picture, and it’s contained in both the Keynotes and SKYtalks.… Read More

Functional Verification using Formal on Million Gate Designs

Verification engineers are the unsung heroes making sure that our smart phone chips, smart watches and even smart cars function logically, without bugs or unintended behavior. Hidden bugs are important to uncover, but what approach is best suited for this challenge?

With the Universal Verification Methodology (UVM) there’s… Read More

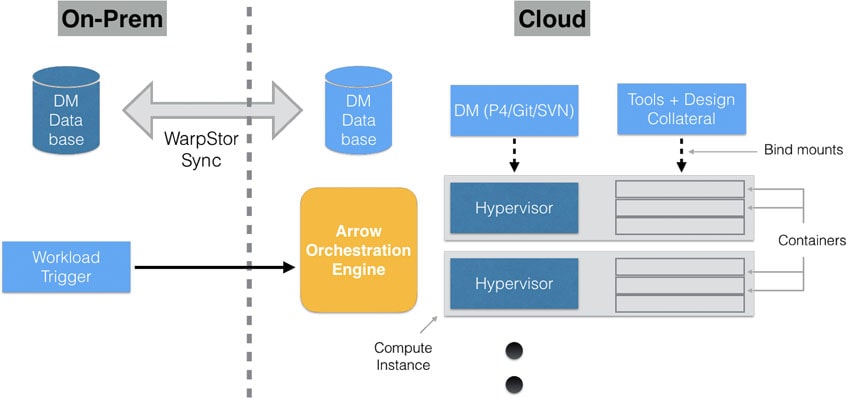

Cloud-based Functional Verification

The big three EDA vendors are constantly putting more of their tools in the cloud in order to speed up the design and verification process for chip designers, but how do engineering teams approach using the cloud for functional verification tests and regressions? At the recent Cadence user group meeting (CDNLive) there was a presentation… Read More

A Smarter Way to Do Multi-Board PCB Systems

Many electronic product ideas start out as sketches on the back of a napkin, then migrate over to diagrams drawn in Visio or PowerPoint, finally entered into EDA-specific tools. With that methodology there’s a big disconnect between the diagrams drawn with a purely graphical tool and the EDA tools, because there’s… Read More

Attend Parts of DAC For Free, Really

The Design Automation Conference (DAC) is the must-see, annual event for semiconductor professionals that design chips, use EDA software, and buy semiconductor IP. Like all conferences there’s an entrance fee, but for the 11th year now you can get a free pass, courtesy of three sponsors: Avatar Integrated Systems, ClioSoft… Read More

Beyond Moore’s Law: High NA EUV Lithography Redefines Advanced Chip Manufacturing