Near the end of any large SoC design project, the RTL code is nearly finished, floorplanning has been done, place and route has a first-pass, static timing has started, but the timing and power goals aren’t met. So, iteration loops continue on blocks and full-chip for weeks or even months. It could take a design team 5-7 days… Read More

Author: Daniel Payne

Why Use PADS Professional Premium for Electronic Design

My IC design career started just a few years before PADS got started in 1985 with a DOS-based tool for PCB design. A lot has changed since then, as PADS was acquired by Mentor Graphics in 2001, and continued to grow under Siemens EDA, now with four versions to choose from, where the top version is called PADS Professional Premium:

- PADS

Clock Aging Issues at Sub-10nm Nodes

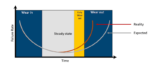

Semiconductor chips are all tested prior to shipment in order to weed out early failures, however there are some more subtle reliability effects that only appear in the longer term, like clock aging. There’s even a classic chart that shows the “bathtub curve” of failure rates over time:

If reality and expectations… Read More

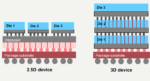

DFT Moves up to 2.5D and 3D IC

The annual ITC event was held the last week of September, and I kept reading all of the news highlights from the EDA vendors, as the time spent on the tester can be a major cost and the value to catching defective chips from reaching production is so critical. Chiplets, 2.5D and 3D IC design have caught the attention of the test world, … Read More

Analyzing Clocks at 7nm and Smaller Nodes

In the good old days the clock signal looked like a square wave , and had a voltage swing of 5 volts, however with 7nm technology the clock signals can now look more like a sawtooth signal and may not actually reach the full Vdd value of 0.65V inside the core of a chip. I’ll cover some of the semiconductor market trends, and then challenges… Read More

Webinar: Post-layout Circuit Sizing Optimization

My IC design career started out with manually sizing transistors to improve performance, while minimizing layout area and power consumption. Fortunately we don’t have to do manual transistor sizing anymore, thanks to EDA tools that are quicker and more accurate than manual methods. MunEDA is an EDA vendor that has developed… Read More

New ECO Product – Synopsys PrimeClosure

New EDA product launches are always an exciting time, and I could hear the energy and optimism from the voice of Manoj Chacko at Synopsys in our Zoom call about Synopsys PrimeClosure. During the physical implementation phase for IC designs there’s a big challenge to reach timing closure, and with advanced nodes the number… Read More

3D IC – Managing the System-level Netlist

I just did a Google search for “3D IC”, and was stunned to see it return a whopping 476,000 results. This topic is trending, because more companies are using advanced IC packaging to meet their requirements, and yet the engineers doing the 3D IC design have new challenges to overcome. One of those challenges is creating… Read More

Die-to-Die Interconnects using Bunch of Wires (BoW)

Chiplets are a popular and trending topic in the semiconductor trade press, and I read about SoC disaggregation at shows like ISSCC, Hot Chips, DAC and others. Once an SoC is disaggregated, the next challenge is deciding on the die-to-die interconnect approach. The Open Compute Project (OCP) started 10 years ago as a way to share… Read More

Machine Learning in the Fab at #59DAC

It used to be true that a foundry or fab would create a set of DRC files, provide them to designers, and then the process yield would be acceptable, however if the foundry knows more details about the physical implementation of IC designs then they can improve the yield. Using a digital twin of the design, process and metrology steps… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?