You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The Design Automation Conference has been the pinnacle for semiconductor design for almost 60 years. This year will be my 38th DAC and I can’t wait to see everyone again. One of the companies I will be spending time with this year is Altair.

Last month Altair acquired our friends at Concept Engineering, the leading provider… Read More

Building a multi-FPGA prototype for SoC verification is complex with many interdependent parts – and is “always on a clock”. The best multi-FPGA prototype implementation is worthless if its not up and running early in the SoC design cycle, where it offers the highest verification ROI terms of minimizing the cost of bug fixes … Read More

Chiplets are hot now as a way to extend Moore’s Law, dividing functionality across multiple die within a single package. It’s no longer practical to jam all functionality onto a single die in the very latest processes, exceeding reticle limits in some cases and in others straining cost/yield. This is not an academic concern. Already… Read More

3D-ICs bring together multiple silicon dies into a single package that’s significantly larger and complex than traditional systems on a chip (SoCs). There’s no doubt these innovative designs are revolutionizing the semiconductor industry.

3D-ICs offer a variety of performance advantages over traditional SoCs. Because … Read More

Recently, in one of my regular check-ins with AMIQ EDA, I was pleased that they linked me up with an active customer. The resulting post summarized my discussion with three engineers from Kepler Communications Inc. They talked about using one of the AMIQ EDA products in the design of FPGAs for space-borne Internet connectivity.… Read More

Intel announced today that they are partnering with cloud and EDA companies to better enable their foundry business. This is a natural extension of the Accelerator ecosystem program announced earlier. More and more chip designs are being done in the cloud and from my experience cloud based designs are better. Some companies use… Read More

Semiconductor manufacturers are under constantly increasing and intense pressure to accelerate innovative new chip designs to market faster than ever in smaller package sizes while assuring signal integrity and reducing power consumption. Three-dimensional integrated circuits (3D-ICs) promise to answer all these demands… Read More

The TSMC Technical Symposium is today so I wanted to give you a brief summary of what was presented. Tom Dillinger will do a more technical review as he has done in the past. I don’t want to steal his thunder but here is what I think are the key takeaways. First a brief history lesson.

The history of TSMC Technology Development with 12 key… Read More

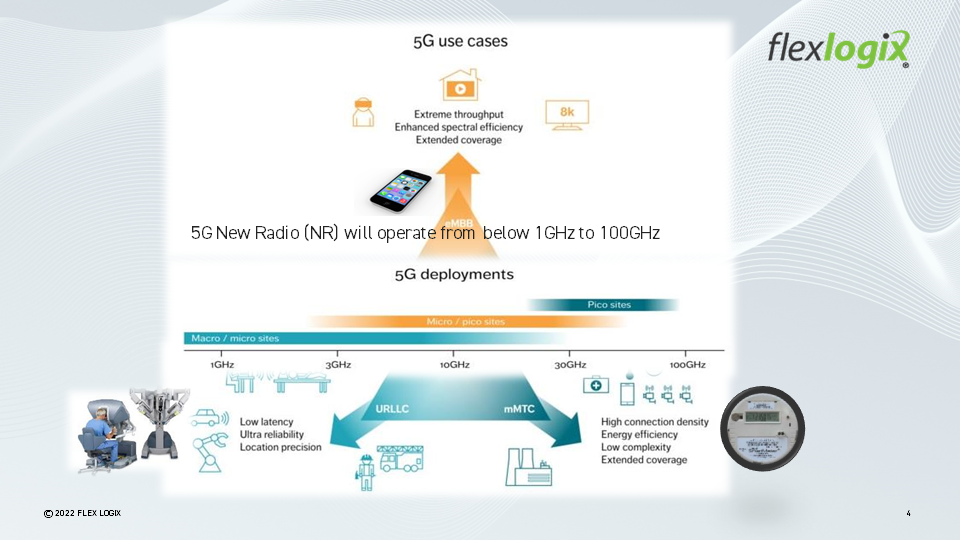

The demands of 5G requires new designs to not only save power but also increase performance and by moving to advance power-saving nodes and by using eFPGAs will help to achieve these goals. This paper will introduce 5G and O-RAN, the complexity of these systems, and how flexibility could be beneficial. Then we will dive into how eFPGA… Read More

One of the recent live events I attended was the 2022 GSA Silicon Leadership Summit on May 12th at the Santa Clara Convention Center (my favorite location). This was the first GSA live event in two years so it was a must attend gathering. This event targets semiconductor ecosystem executives (200+ people attended) so there were many… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era