You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

A Most Significant Manby Beth Martin on 11-06-2012 at 8:10 pmCategories: EDA, Siemens EDA

Most of us live perfectly good lives without distinction, fame, or note. Others rack up the honors, filling their walls and resumes with recognition of their brilliance. Like Dr. Janusz Rajski.

Rajski is the director of engineering for the test products at Mentor Graphics, an IEEE Fellow, and the inventor of embedded deterministic… Read More

A Brief History of Mentor Graphicsby Beth Martin on 08-20-2012 at 11:00 pmCategories: EDA, Siemens EDA

In 1981, Pac-Man was sweeping the nation, the first space shuttle launched, and a small group of engineers in Oregon started not only a new company (Mentor Graphics), but an entirely new industry, electronic design automation (EDA).

Mentor founders Tom Bruggere, Gerry Langeler, and Dave Moffenbeier left Tektronix with a great… Read More

Higgs bosons, (un)certainty, and black holesby Beth Martin on 07-18-2012 at 9:00 pmCategories: General

Ever since the announcement in early July from CERN that they likely have, probably, finally found the Higgs boson, I’ve been thinking about what quantum mechanics means to our daily ‘classical model’ existence. On the surface, nothing. The most fantastical aspects of quantum mechanics, like uncertainty, tunneling and the … Read More

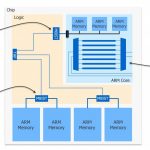

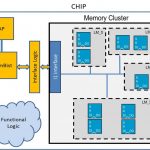

Benjamin Franklin, “I didn’t fail the test, I just found 100 ways to do it wrong.” I was reminded of this line during a joint Mentor-ARM seminar yesterday about testing ARM cores and memories. The complexity of testing modern SoC designs at advanced nodes, with multiple integrated ARM cores and other IP, opens up plenty of room for… Read More

If you are involved in testing memory or logic of ARM-based designs, you’ll want to attend this free seminar on July 17, 2012 in Santa Clara. Mentor Graphics and ARM have a long standing partnership, and have optimized the Mentor test products (a.k.a Tessent) for the ARM processors and memory IP.

The lunch seminar runs from 10:30-1:00… Read More

IC Test Sessions at SEMICON West 2012by Beth Martin on 07-02-2012 at 1:43 pmCategories: EDA, Siemens EDA

SEMICON West is coming up this July 10-12 at the Moscone Center in San Francisco. It covers a broad swath of the microelectronics supply chain, but I was particularly interested in the test sessions. Here are two that I recommend.

“The Value of Test for Semiconductor Yield Learning” on Tuesday, July 10, at 1:30p. The… Read More

It takes an act of Congress…by Beth Martin on 06-19-2012 at 4:29 pmCategories: Uncategorized

Foreign students earn roughly two-thirds of the total engineering Ph.D.s earned in the U.S., yet there is no policy to allow, let alone encourage, them to stay in the U.S. after graduation. I was aware of this problem 14 years ago when I started working in EDA, but haven’t paid much attention since then.

So, I scoured the congressional… Read More

Conquering the Big Data Challengesby Beth Martin on 04-02-2012 at 4:38 pmCategories: EDA, Siemens EDA

Extrapolating the trends from last 20 years to the next ten suggests that we will be implementing a trillion transistors or more by 2020. At 20nm, with the chip sizes touching billions of transistors, the age old problem of how to implement a design in the most efficient manner remains unanswered. … Read More

DFM Industry Surveyby Beth Martin on 02-10-2012 at 1:28 pmCategories: EDA, Siemens EDA

As part of the DFM Conference at the SPIE Advance Lithography symposium, the DFM committee is conducting an informal survey on the current state of Design For Manufacturability in the Semiconductor Industry.

Please take this anonymous 16 question survey to identify critical Design for Manufacturability (DFM) issues facing… Read More

DFM at SPIE Advance Litho showby Beth Martin on 02-09-2012 at 6:40 pmCategories: EDA, Siemens EDA

This year’s SPIE Advanced Lithography is loaded with interesting keynotes and sessions. To help me narrow down what to see, I spoke with John Sturtevant. John is co-chair of the Design for Manufacturability through Design-Process Integration conference, and the director for technical marketing for RET products at Mentor Graphics.… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?