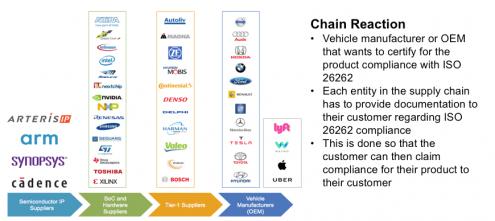

Everyone up and down the electronics supply chain is jumping on the ISO 26262 bandwagon and naturally they all want to show that whatever they sell is compliant or ready for compliance. We probably all know the basics here – a product certification from one of the assessment organizations, a designated safety manager and a few other… Read More

Author: Bernard Murphy

Semiconductor, EDA Industries Maturing? Wally Disagrees

Wally Rhines (President and CEO of Mentor, A Siemens Business) has been pushing a contrarian view versus the conventional wisdom that the semiconductor business, and by extension EDA, is slowing down. He pitched this at DVCon and more recently at U2U where I got to hear the pitch and talk to him afterwards.

What causes maturing is… Read More

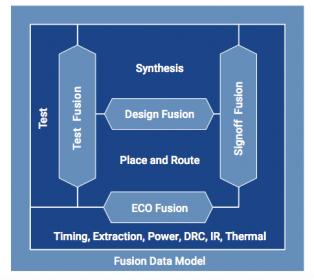

Retooling Implementation for Hot Applications

It might seem I am straying from my normal beat in talking about implementation; after all, I normally write on systems, applications and front-end design. But while I’m not an expert in implementation, I was curious to understand how the trending applications of today (automotive, AI, 5G, IoT, etc.) create new demands on implementation,… Read More

Webinar: Thermal and Reliability for ADAS and Autonomy

OK, so maybe the picture here is a little over the top, but thermal and reliability considerations in automotive in general and in ADAS and autonomy in particular, are no joke. Overheating, thermal-induced EM and warping at the board-level, in the package or interposers, are concerns in any environment but especially when you’re… Read More

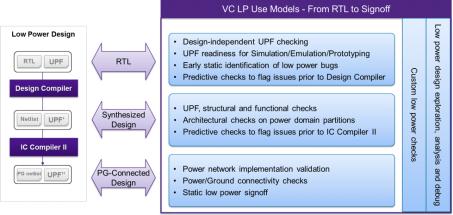

Low Power Verification Shifting Left

I normally think of shift left as a way to move functional verification earlier in design, to compress the overall design cycle. But it can also make sense in other contexts, one particularly important example being power intent verification.

If you know anything about power intent, you know that it affects pretty much all aspects… Read More

Formal Signoff – a Cisco Perspective

The second segment of Oski’s most recent “Decoding Formal” event was a talk by Anatoli Sokhatski (formal tech lead at Cisco) on training and methodology development for a structured and scalable approach to formal verification, particularly with emphasis on formal signoff.

Anatoli stressed that he and others in the team did … Read More

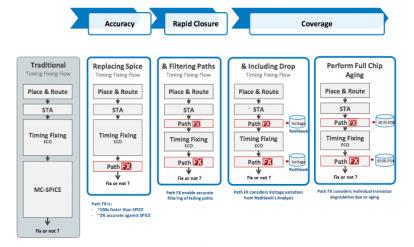

Peering Over the Timing Edge

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More

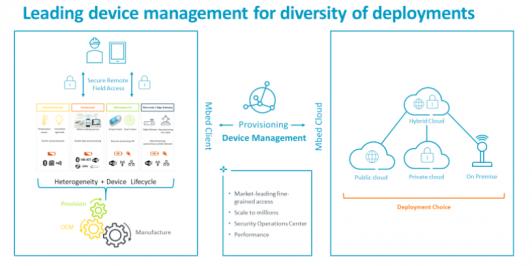

ARM IoT Mbed Update

Normally press release events with ARM tend to be somewhat arms-length – a canned pitch followed by limited time for Q&A. Through a still unexplained calendar glitch I missed a scheduled call for a recent announcement. To make up I had the pleasure of a 1-on-1 with Hima Mukkamala, GM of IoT cloud services at ARM. Hima is a heavy … Read More

Safety in the Interconnect

Safety is a big deal these days, not only in automotive applications, but also in critical infrastructure and industrial applications (the power grid, nuclear reactors and spacecraft, to name just a few compelling examples). We generally understand that functional blocks like CPUs and GPUs have to be safe, but what about the … Read More

Functional Safety in Delhi Traffic

While at DVCon I talked to Apurva Kalia (VP R&D in the System and Verification group at Cadence). He introduced me to the ultimate benchmark test for self-driving – an autonomous 3-wheeler driving in Delhi traffic. If you’ve never visited India, the traffic there is quite an experience. Vehicles of every type pack the roads … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?