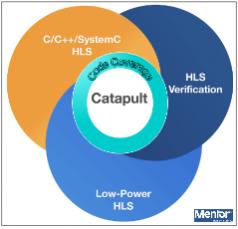

Coverage is a common metric with many manifestation. During the ‘90s, both fault and test coverage were mainstream DFT (Design For Testability) terminologies used to indicate the percentage of a design being observable or tested. Its pervasive use was then spilled over into other design segments such as code coverage, formal… Read More

Author: Alex Tan

Closing Coverage in HLS

LightSuite – Physical Design Goes Photonics!

Light is a form of energy. It reveals an object’s color and shape through the refraction (passing through light) or the reflection (bouncing back light) of its beam. While photon is the smallest measure of light, the term photonicscan be defined as the science and technology of generating, controlling, and detecting photons. … Read More

Data Management for SoCs – Not Optional Anymore

Design Management (DM) encompasses business decisions, strategies and processes that enable product innovations. It is the foundation for both effective collaboration and gaining competitive advantage in the industry. This also applies in the high-tech space we are in, as having a sound underlying SoC data management for… Read More

Apogee Pipelining in Real Time

Pipelining exploits parallelism of sub-processes with intent to achieve a performance gain that otherwise is not possible. A design technique initially embraced at the CPU micro-architectural level, it is achieved by overlapping the execution of previously segregated processor instructions –commonly referred … Read More

Fuzzing on Automotive Security

The ECU. That was the service department prognosis on the root cause of thealways-on air bag safety light on my immaculate car. Ten years ago the cost for its replacement with after market part was at par with getting a new iPhone 8. Today, we could get four units for the same price and according to data from several research companies,… Read More

DesignWare IP as AI Building Blocks

AI is disruptive and transformative to many status quos. Its manifestation can be increasingly seen in many business transactions and various aspects of our lives. While machine learning (ML) and deep learning (DL) have acted as its catalysts on the software side, GPU and now ML/DL accelerators are spawning across the hardware… Read More

Harnessing Clock and Power

Switching translates to power. Similar to the recent slow down experienced by Moore’s Law, the constant power density (power demand per unit chip area) prescribed by Dennard scaling was no longer affordable across the technological scaling. While the contribution of leakage power component in advanced process nodes was getting… Read More

Enabling Complex System Design Environment

Deterministic, yet versatile. Robust and integrated, yet user-friendly and easily customizable. Those are some desirable characteristics of an EDA solution as the boundaries of our design optimization, verification and analysis keep shifting. A left shift driven by a time-to-market schedule compression, while the process… Read More

A True Signoff for 7nm and Beyond

The Tale of Three Metrics

Meeting PPA (Performance, Power and Area) target is key to a successful design tapeout. These mainstream QoR (Quality of Results) metrics are rather empirical yet inter-correlated and have been expanded to be linked with other metrics such as yield, cost and reliability. While the recent CPU performance… Read More

Enhancing Early Static FSM

Finite state machines (FSMs) are widely adopted as part of reactive systems to capture their dynamic behaviors using a limited number of modes or states that usually change according to the applied circumstances. Some terminologies are frequently used to describe the FSM characteristics: state, transition, condition and … Read More

Solving the EDA tool fragmentation crisis