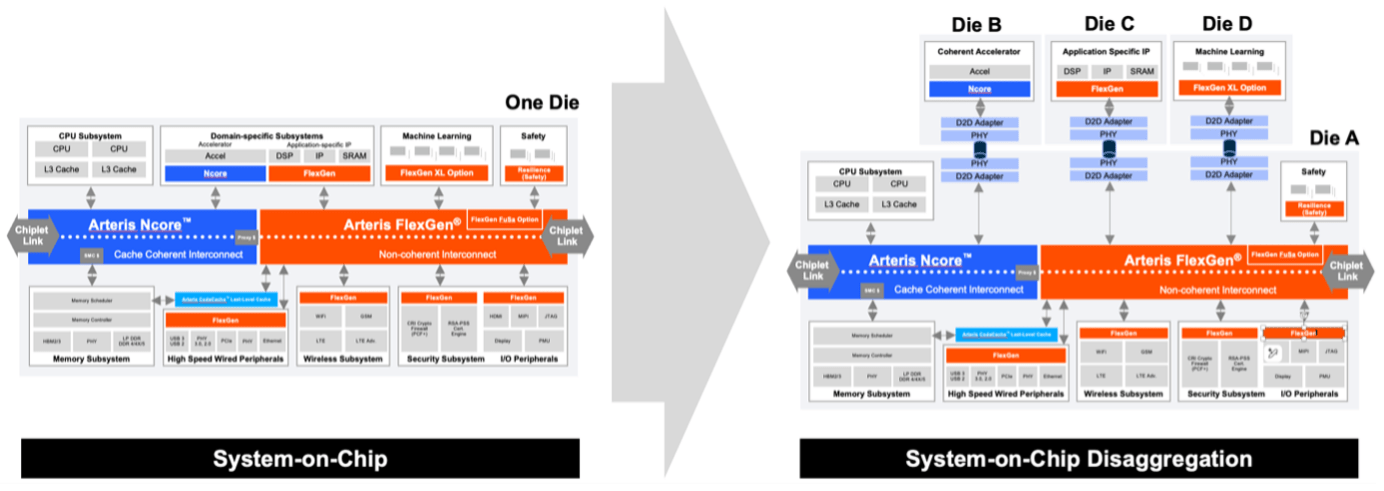

In chiplet-based design we continue the march of Moore’s Law by scaling what we can put in a semiconductor package beyond the boundaries of what we can build on a single die. This style is already gaining traction in AI applications, high performance computing, and automotive, each of which aims to scale out to highly integrated systems meeting performance, power, cost, and reliability goals. The technology challenge then is to build effective communications infrastructure between those chiplets.

UCIe is mentioned frequently as the standard for connectivity between chiplets. That standard is important, but is only the bottom layer of the communication stack. In the modern era of networks-on-chip (NoCs), modern networks must also handle packetized communication, congestion, and quality of service, within chiplets and between chiplets. This prompts a deeper dive into Arteris’ recently announced collaboration with AMD, in which FlexGen smart NoC IP cooperates with AMD’s Infinity Fabric. Commercial and proprietary network co-existence has arrived.

Commercial NoC IP jumps a hurdle

For a long time NoC IP choices were an either/or decision. Build and use your own in-house NoC IP or buy a commercial IP. The choice was easy for new ventures or design teams who had outgrown earlier in-house options and who prioritized differentiation in core functions rather than in the communication fabric. Buy a commercial option from an IP supplier and work with that vendor to ensure they keep up as requirements evolved. Still, some semiconductor houses, particularly the big compute vendors like AMD and Intel, continue to see value in their proprietary NoC IP and were not obvious candidates for a commercial option.

Chiplet-based design seems to have scaled that wall. Highly optimized in-house communication IPs such as Infinity Fabric continue to be central in coherent compute chiplets but now AMD’s endorsement of using FlexGen smart NoC IP between chiplets has shown co-existence to be a very viable option.

Andy Nightingale (VP Product Management and Marketing at Arteris) told me that the term IO Hub is now commonly used to represent an emerging architectural pattern, a structure to bridge coherent fabrics (such as Infinity Fabric) with heterogeneous subsystems. A new realization that one unified fabric architecture may not be the optimal strategy across chiplet-based systems.

I asked Andy why some of their top-tier customers are turning to Arteris for this capability. Why not just build their own IO Hub? Their answer reflects what you’ll often hear when design houses choose a commercial solution over an in-house option. They want to prioritize in-house resources towards their core competencies, using a proven partner to handle off-chiplet communication. A co-existence solution meets that objective.

Digging a little deeper

The physical connectivity between chiplets will most commonly be wires, not active elements (also possible but that style of connectivity is more expensive I am told). Traffic management through the IO Hub is therefore handled through distributed control from chiplet interfaces (network interface units for Arteris IPs) to the hub. In the IO hub use-case FlexGen is optimized for non-coherent, high-bandwidth data flows like HBM, PCIe, and AI accelerators.

Effectively managing this structure – off-chip interconnect topology, adding buffers/ adapters, scaling wide datapaths, managing QoS, is a complex task that will probably demand iteration as the larger design evolves. That task usually must be handled by a senior NoC designer, consuming weeks of effort. Arteris’ FlexGen smart NoC technology acts as a virtual senior NoC engineer to automate this function, providing when compared with manual design up to 10x productivity improvement, 30% shorter wirelength and 10% reduced latency according to announced customer benchmarks.

Expanding Arteris reach

Arteris’ FlexGen NoC IP for non-coherent networks and Ncore for coherent networks are already well-established, particularly in new ventures, AI, automotive and many other applications. Arteris have announced a range of co-existence collaborations including:

- Adoption by AMD to augment Infinity Fabric for AI chiplets

- Accepted in the Intel Foundry AI + Chiplet Alliance

- Adopted by Samsung LSI to use FlexNoC/FlexGen alongside proprietary fabric in mobile and AI SoCs

- Adopted by NXP using Ncore and FlexNoC for automotive, integrating safety and accelerators in ASIL D systems

- Publicly announced benchmarks from SiMa.ai showing increased productivity and reduced wirelengths

It’s now quite clear that Arteris can now augment proprietary NoC solutions in addition to providing comprehensive NoC fabric solutions, as already demonstrated in widespread adoption in multiple markets. Impressive. You can learn more about Arteris HERE.

Also Read:

Arteris Simplifies Design Reuse with Magillem Packaging

Arteris at the 2025 Design Automation Conference #62DAC

Arteris Expands Their Multi-Die Support

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.