I am tracking the shift to multi-die design, so it’s good to see Arteris extend their NoC expertise, connecting chiplets across an interposer. After all, network connectivity needs don’t stop at the boundaries of chiplets. A multi-die package is at a logical level just a scaled-up SoC for which you still need traffic routing and management between those subsystem chiplets. Arteris just took the covers off their Multi-Die Solution response: complete coherent and non-coherent connectivity support, on-chiplet and between chiplets, Magillem Connectivity for system partitioning and Magillem Registers for memory map integration between chiplets. This is what I wanted to see.

The Market

Arteris (Ashley Stevens, Director PM at Arteris, and Andy Nightingale, VP PM) shared some interesting stats on growth in the global chiplets market, estimated at between $107B and $373B by 2033 with compound annual growth rates of between 76% and 95%. It should be obvious from these numbers that extrapolating from current few $B numbers involves a good deal of guess work, but what is clear is that the chiplet market is anticipated to grow fast. Andy has seen numbers suggesting the current $ volume is around 2% of the conventional semiconductor volume, tiny today but lots of headroom to grow.

Clearly the drivers for this growth will be the big semi/system houses, the hyperscalers with their in-house development (many-core servers, AI servers, advanced networking, storage, etc), automotive/transportation, wireless infrastructure, even maybe robotics. Each connecting multiple subsystems through a network in a multi-die package. I’m guessing not edge consumer applications anytime soon, but who knows in these fast-moving times.

Connectivity

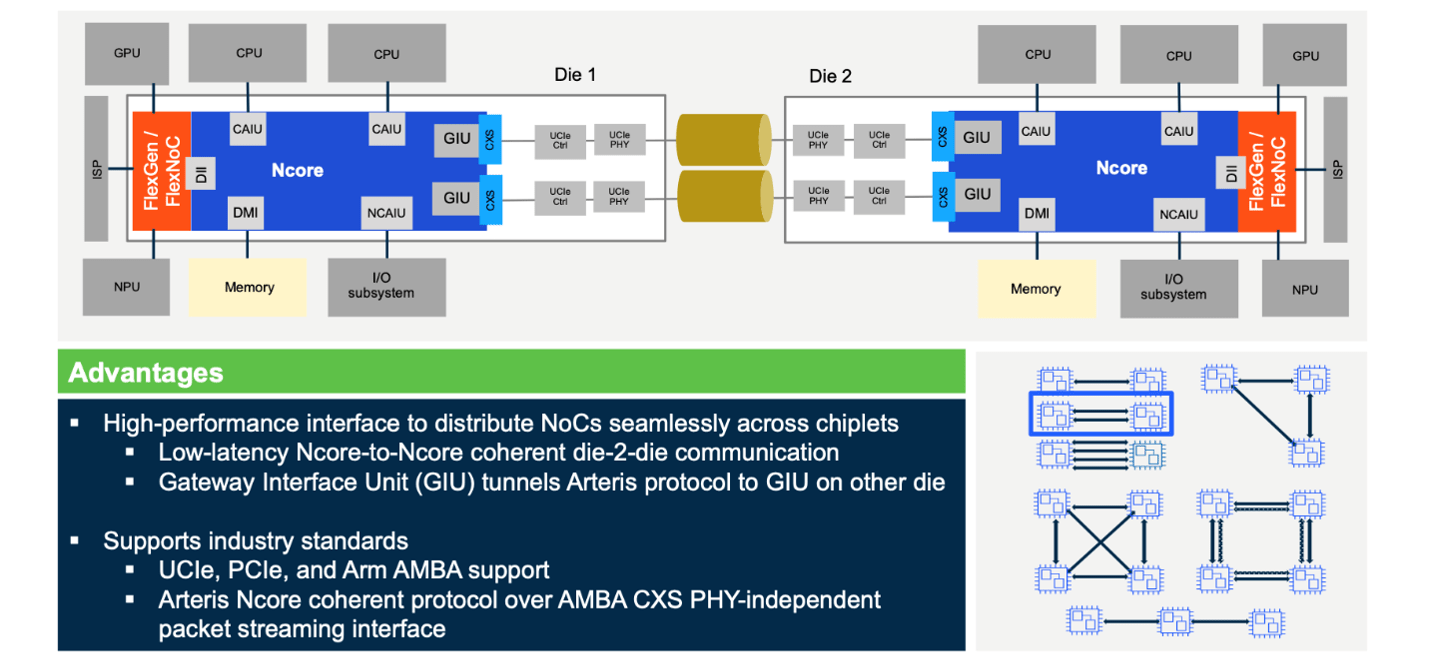

Again, any multi-die design is just a giant design which happens to be partitioned into chiplets, with such traffic communication between chiplets as is demanded by the application. An example might be a many-core server split across say 4 chiplets, each chiplet hosting perhaps 32 CPUs on a mesh network. That mesh communication must continue up to the inter-chiplet level, crossing from chiplet to chiplet through connections on the interposer. The mechanism to cross between chiplets requires some special buffering to accommodate inter-die transitions but otherwise can continue the same logical mesh connectivity.

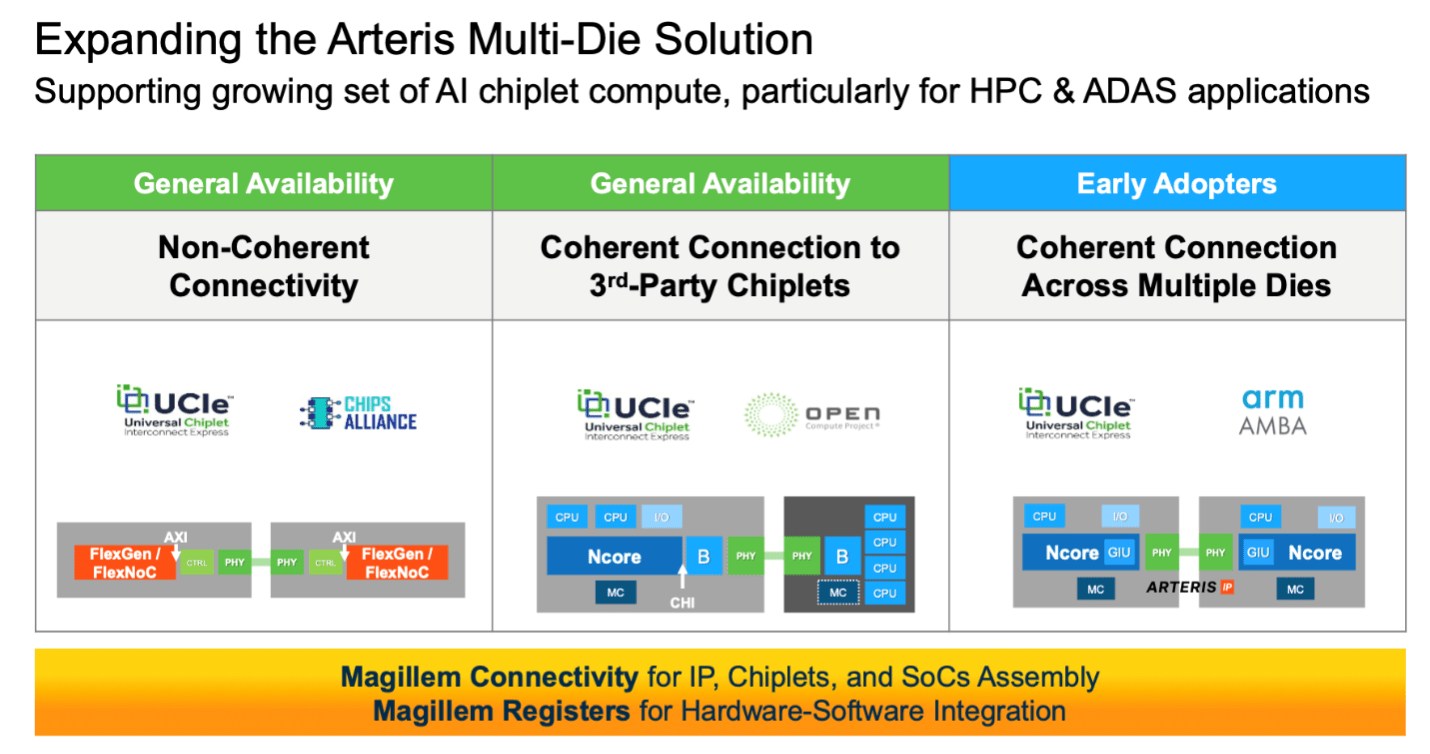

Arteris has been the leading commercial provider for on-chip non-coherent and coherent connectivity IP for many years now and have built a very respectable list of customers across all major markets. Those same product lines (FlexNoC for non-coherent and Ncore for coherent) have been extended to provide multi-die support. The technology offers significant flexibility in inter-chiplet connections, supporting multiple options, from point to point, to mesh, even IO hub.

These NoCs are proven against industry standards for inter-die communication, especially the UCIe interfaces from Cadence and Synopsys. Arteris add gateway interface units (GIUs) to front-end network communication prior to UCIe.

Partitioning and multi-die memory map

Ashley and Andy made a big deal about the role the Magillem Connectivity and Magillem Register tools play in the development flow and at first I was confused. Surely all or most of the chiplets are pre-defined so the partitioning is already fixed? However Arteris are already seeing customers want to do something different. They’ll start with a prior design and want to scale that out by replication of big functional blocks into one mega design (in RTL), ignoring manufacturing constraints. They use this to experiment to find an optimum partitioning (throughput, etc.) before implementing the partitioning. Which on reflection makes complete sense today. Today’s commercial chiplet market is very nascent and much of the value in chip makers designs is proprietary. Of course many of their chiplets will be built on their own design IP, replicated as needed in their scale out architectures.

The re-partitioning step I remember from my previous life. Sounds simple in principle but it proves to be amazingly fiddly and full of potholes if you aren’t careful. The Magillem Connectivity solution has been in production for a long time and provides exactly this capability.

Need for the Magillem Register solution is immediately obvious. A multi-die implementation must combine multiple chiplets, each with its own register interfaces and memory map, consolidating into one big memory map for the full multi-die system. This isn’t just a question of HW/SW interface documentation, test and other collateral. The NoC itself is configured by the memory offsets determined for each chiplet, intimately tied with the ultimate memory map. These hardware and software factors can and should be managed together.

It’s good to see these connectivity and register capabilities fold so neatly into multi-die design!

Takeaway

I was expecting/hoping for this advance and now it’s here. Arteris are already claiming success in partnering with Rebellions, Tenstorrent, and Menta as early adopters of their multi-die non-coherent solution. They are also saying that both coherent and non-coherent solutions are now available.

You can read more HERE.

Also Read:

How Arteris is Revolutionizing SoC Design with Smart NoC IP

Podcast EP277: How Arteris FlexGen Smart NoC IP Democratizes Advanced Chip Design with Rick Bye

Is Arteris Poised to Enable Next Generation System Design?

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.