Load-pull power amplifier (PA) design techniques determine the optimal impedances at the power transistor’s extrinsic reference plane, which is the physically accessible boundary for measurement or simulation. This reference plane can be the package transistor leads, die bond pads, or IC chip terminals. It includes… Read More

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More

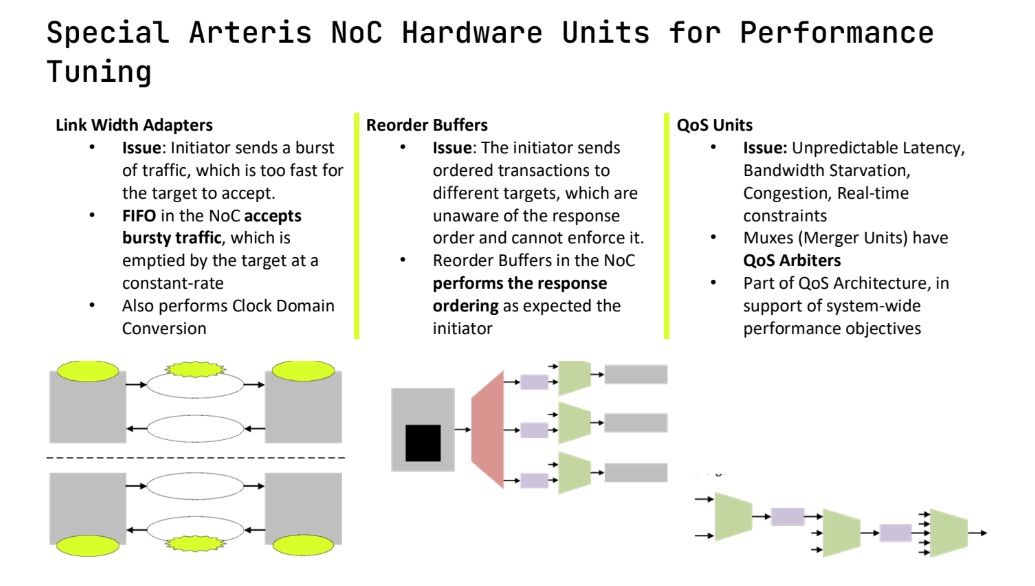

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More

NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More From Wooden Boards to White Gloves: How FPGA Prototyping and Emulation Became Two Worlds of Verification… and How the Convergence Is UnfoldingFPGA prototyping and hardware emulation originated from two…Read More

From Wooden Boards to White Gloves: How FPGA Prototyping and Emulation Became Two Worlds of Verification… and How the Convergence Is UnfoldingFPGA prototyping and hardware emulation originated from two…Read More When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read MoreAnalog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology Symposium

Analog Bits has a way of stealing the show at every event they attend. The formula is actually quite straight-forward – come to the show with the most relevant, highest impact IP running on the most advanced process. The company will be applying this strategy again at the upcoming TSMC 2026 Technology Symposium with an array of real-time… Read More

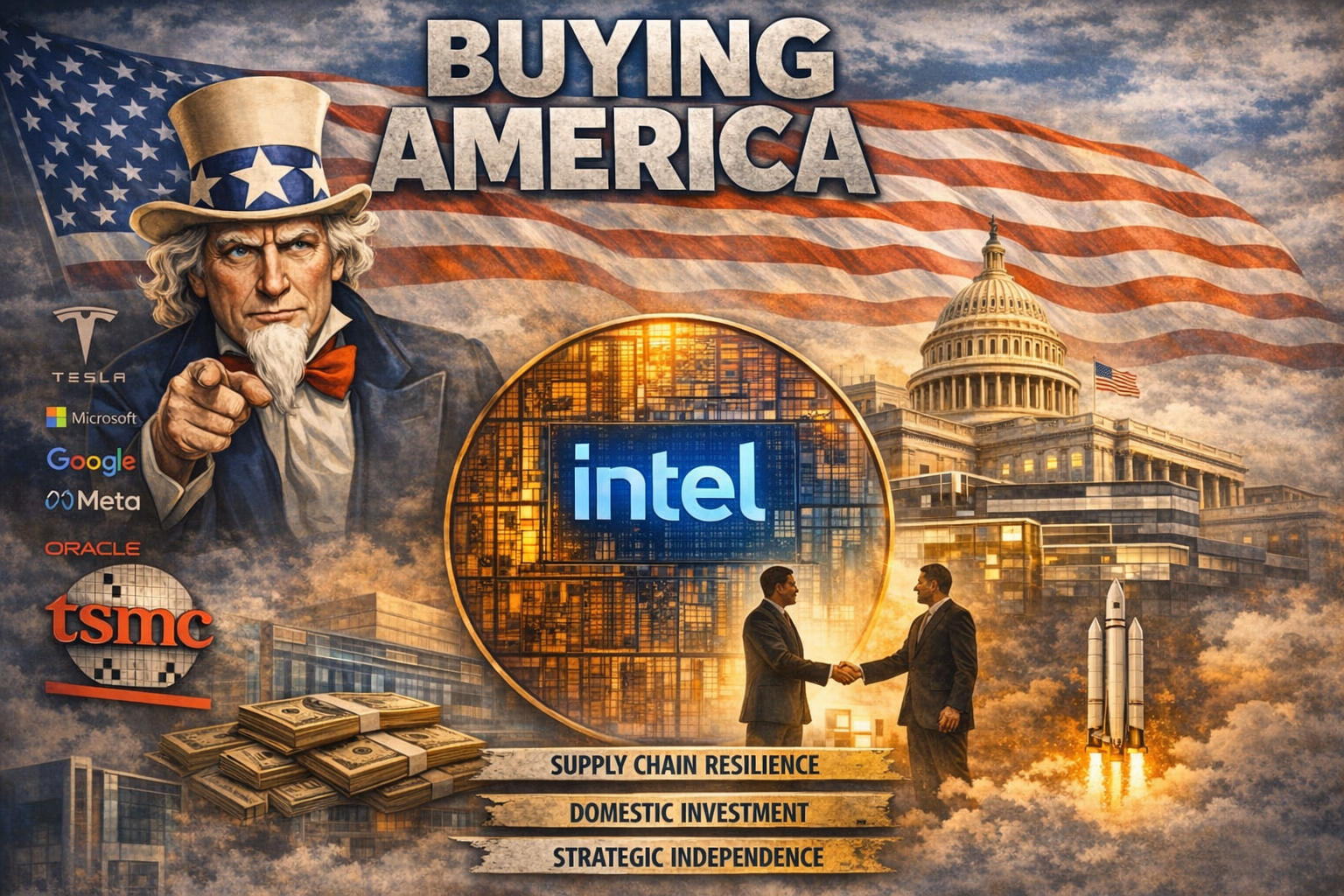

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint

SambaNova Systems and Intel have introduced a blueprint for heterogeneous inference that reflects a significant shift in how modern large language model (LLM) workloads are deployed. Instead of relying on a single accelerator type, the proposed architecture assigns different phases of inference to specialized hardware:… Read More

CEO Interview with Johan Wadenholt Vrethem of Voxo

With over two decades of experience bridging technology and business, Johan Wadenholt Vrethem focused on harnessing AI to transform how organizations operate and engage with their customers. After leading critical digital initiatives and client engagements in the banking and finance sectors at CGI, Johan co-founded Voxo… Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!

The opening of the TSMC 2026 earning call series brought no surprises. CC Wei has done more than 30 such calls since taking the CEO position in 2018 and he never fails to disappoint. Once again, CC Wei reported numbers above guidance driven by strong demand and flawless execution. This illustrates the benefit of TSMC’s close collaborations… Read More

Podcast EP342: The Evolution and Impact of Physical AI with Hezi Saar

Daniel is joined by Hezi Saar, Executive Director of Product Marketing at Synopsys, Hezi is responsible for the mobile, automotive, and consumer IP product lines. He brings more than 20 years of experience in the semiconductor and embedded systems industries.

Dan explores the growing field of physical AI with Hezi, who explains… Read More

Speculation: Silicon’s Most Expensive Compulsion

How Time-Based Scheduling

Reclaims Silicon Wasted by Speculative Execution

By: Dr. Thang Tran, Founder and CTO, Simplex Micro

I have spent my career designing processor architectures, and I have reached an uncomfortable conclusion: a substantial fraction of the silicon area and power in modern high-performance processors… Read More

WEBINAR: Beyond Moore’s Law and The Future of Semiconductor Manufacturing Intelligence

This is a live panel with industry experts who are on the leading edge of AI in semiconductor manufacturing. This is a must attend event for all levels of semiconductor professionals. I hope to see you there.

The semiconductor industry faces unprecedented challenges as it pushes toward advanced nodes below 3nm, managing exponential… Read More

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White Paper

Review the specifications of any state-of-the-art microcontroller and you will discover the high dynamic current the device can consume. Examining the high clock rates and low tolerable voltage drop will lead you to the all-important power delivery network, or PDN. Components here include power planes, layer stack-up, decoupling… Read More

Podcast EP341: Details of the Upcoming Microelectronics US Event with Michael Adeniya

Daniel is joined by Michael Adeniya, Group Director, Microelectronics Global and a key architect behind the launch of Microelectronics US. Mike is focused on uniting the “Silicon Hills” ecosystem to address the practical engineering bottlenecks of the post CHIPS Act era. By fostering strategic partnerships … Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint