Easy-Logic Technology has always kept “creating disruptive algorithms for functional ECO” in mind, adhering to the motto of “customer trust, technology leadership, and service first”, to pursue ultimate customer satisfactions.

Easy-Logic advocates the simple principle of product superiority. We treat customer compliments as our product achievement, and customer’s word of mouth has been our best business propellant.

Globalization is one of Easy-Logic’s short-term goals. Easy-Logic has collaborated with more than 30 ASIC design companies worldwide in building up a more efficient design flow, and we strive for being recognized as a top technology company in two years.

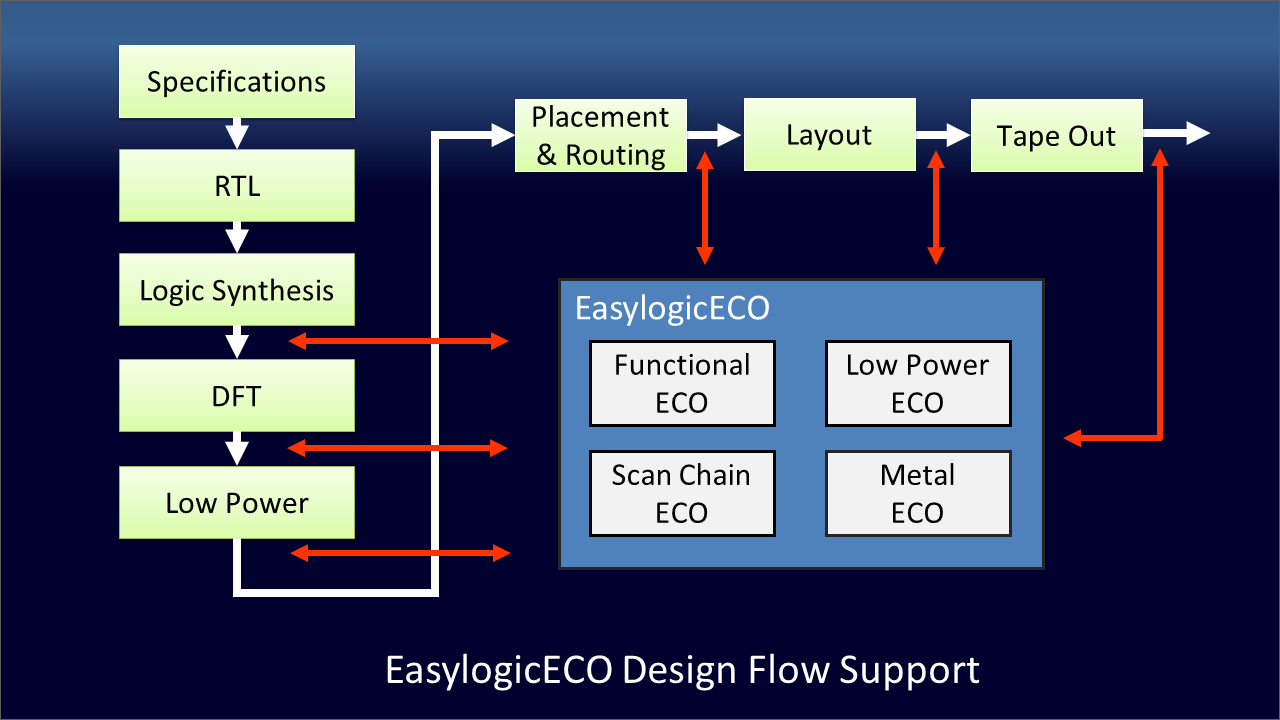

Easylogic’s ECO solution suite includes two products – EasylogicECO and EasylogicDU:

Pre-Mask ECO

A Pre-Mask ECO is that you make changes to a design that is not yet committed to place & route of the chip layout.

The changes made in RTL code has ripple effects on function verification, timing delay, static timing, formal verification, and DFT. Even though less resource constraints imposed, Pre-Mask ECO tasks often seriously impact the design schedule. Easy-Logic provides a solution that is optimized for all the impacted design areas.

Post-Mask ECO

A Post-Mask ECO is that you make changes to a design that is already at, or after, the place & route stage. The reasons could be a functional bug found in the FPGA prototyping, or during testing the sample chip.

The changes in RTL code not only impact all the factors in a Pre-Mask ECO job, but also are restricted to metal fixes using spare cells, filler cells, or gate array, reserved for ECO purpose.

Design Upgrade

ECO needs occur even after chips are successfully introduced to the market. A common example is to adopt a new functional block, such as a more recent version of IP which runs at a higher frequency, on the existing design. This type of ECO is evolving into a critical design method to further strengthen the product competitiveness.

In such cases, the scale of the RTL change is not limited to a few lines of code, and the size of patch might be way over tens of thousands of gates (or instances). Easylogic provides a solution that meets the project needs.

Design Solutions

The critical success factor for all three ECO scenarios is preserving the existing design as much as possible to reduce the size of the ECO patch. Easylogic offers a unique design solution for each application scenarios. Please click the picture below to connect to the solution.

Comments

There are no comments yet.

You must register or log in to view/post comments.