SEMICON West is coming up this July 10-12 at the Moscone Center in San Francisco. It covers a broad swath of the microelectronics supply chain, but I was particularly interested in the test sessions. Here are two that I recommend.

“The Value of Test for Semiconductor Yield Learning” on Tuesday, July 10, at 1:30p. The focus of this presentation by Geir Eide, the manager of yield learning products at Mentor Graphicsis, is on using software-based diagnosis of test failures to find the defect type and location of failures “based on the design description, scan test patterns, and tester fail data.” Advanced techniques like the “diagnosis-driven yield analysis” he describes are becoming necessary with the emergence of design-sensitive defects. He’ll cover two of my favorite things: DFM-aware yield analysis, and machine learning techniques that allow for keen statistical analysis of diagnosis data. As a side note, if you are interested in test and yield issues, Semiwiki has a new forum on the topic.

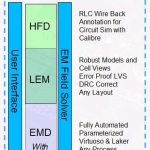

On Wednesday, we get the greatest hits of the most recent International Test Conference ITC). It starts with Friedrich Hapke, the director of engineering for silicon test at Mentor Graphics in Germany reprising a popular ITC paper, “Cell-aware Analysis for Small-delay Effects and Production Test Results from Different Fault Models.” He describes how to find defects inside of standard cells. This “cell-aware” testing greatly improves overall defect coverage. He will show industrial results (from AMD) on 45nm and 32nm designs to support that claim.

Cell-aware testing uses user defined fault models (UDFM), and you can learn about that

from this Mentor whitepaper, User Defined Fault Models.

After taking in all the interesting test and yield analysis sessions, be sure to mosey over to the show floor for happy hour refreshments, and to tell me what you found most interesting. Happy hour is Wednesday at 3:30. Don’t forget to register for SEMICON West.