Semiconductor IP re-use enables modern SoC designs to be realized in a timely fashion, yet with hundreds of IP blocks in a chip the chances are higher that an error in any IP block could cause the entire system to fail. At advanced nodes like 28nm and smaller, the number of Process, Voltage and Temperature (PVT) corners is increasing to account for the variability.

Qualification of each cell or IP block is then critical to ensure a correct by construction methodology. There are several modeling formats used for IP blocks:

ECSM Timing Model

To ensure the quality of these models you should be checking:

- Are all arcs populated with data?

- Is the data trustworthy?

- Do the arcs match what is found in the cells’ functional model?

- Does the data track with capacitance and temperature?

Fractal Technologiesis an EDA company with a validation tool called Crossfire designed to answer exactly these types of IP quality questions.

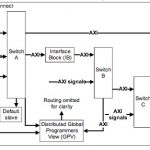

A design engineer would run the Crossfire tool during the characterization flow and would define a golden reference like a Verilog model or a standardized cell-definition format. The timing arcs shown previously in the ECSM timing model are validated against the reference model. This validation process can be fully automated and by embedding Crossfire into the characterization flow you will gain confidence that the model data is trusted.

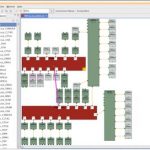

An example output qualification report from running Crossfire is shown below:

This report shows both errors and warnings for all quality checks. You even get to see which checks were waived by your IP provider and decide if you agree with them. Additional reports show documentation like: data sheet, terminals, functional model and delay arcs.

The Crossfire Diagnose Option lets you visually traverse all checks to see errors that can be clicked on as hyperlinks, and the error is then highlighted in the appropriate file or database. This feature really speeds up your understanding of what is wrong with your IP without having to be familiar with structure of the IP.

Another way to use the Crossfire tool is during the IP design flow:

In this flow you would run Crossfire checks on your IP block or component before checking it in. This would catch any inconsistency early in the design process when changes are easier and less time consuming to implement. You could even include Crossfire in nightly QA checks.

Summary

Validating IP and libraries is critical to achieving a correct by construction SoC design flow that works. Quality checks can be run both during the handoff of IP and cell libraries, plus during the IP design flow itself. Fractal Technologies is focused on automating these important quality checks. For more details, read the White Paper: Correct by Construction Design Using Crossfire.

More articles by Daniel Payne…

lang: en_US