MEMS design and fabrication is highly complex in the sense that the fabrication process heavily depends on the design, unlike IC fabrication which has a standard set of processes. A slight change in MEMS design can alter its fabrication steps to a large extent. For example, setting device parameters such as capacitance or linear displacement can affect the choice of the film thickness, etch rate, sidewall profile and so on. The design and process are so much tied together that many iterations through the fab are required (which consume costly resources and time) in order to get a perfect build. While an IDM has to keep its fab resources deployed for such a build-and-test experimentation in-house, a fabless design house has to additionally incur time for its design to take several tours through an external fab. This all has significant impact, first on cost of design and manufacturing and then turn-around-time, thus squeezing the window of opportunity which is already small in today’s competitive semiconductor market.

In such a scenario, there is nothing like having a software tool at the designer’s desk which can provide a 3D model of the complete MEMS device based on its layout and process description. The iterations between the design and the process can take place virtually at the terminal itself until the final model of the device is perfect to enter the fab for manufacturing.

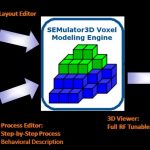

I am impressed with the SEMulator3D Virtual Fabrication Platform from Coventorwhich simplifies this build-and-test cycle for MEMS in the most economical and fastest way through its Voxel Modeling Engine and virtual metrology operations for measurement of critical technology parameters. Above is an example of RF Tunable Capacitor model derived from its layout and process behavior, which has its actuation part in silicon wafer (black block on top) bonded on the RF part in glass wafer (yellow and white block at bottom).

How do you describe the process and metrology steps through the process editor? Above is the edited process file for the RF Tunable Capacitor. It has steps defined similar to a real fabrication flow. Several measurement types can be defined such as CD (critical dimension), difference between max and min elevation, thickness of films at particular locations, angle of a sloped sidewall and so on.

SEMulator3D can show a cross section of the device model at any location. In the above cross section of a RF Tunable Capacitor, CD (finger width of the comb drive), Film Thickness (structure thickness) and Line to Line Spacing (width of the perforation plate) are shown. The virtual metrology measurement options provide ‘3D DRC’ for validating these dimensions. Particular regions (e.g. Comb drive fingers stator and rotor Line-to-Line) can be selected to view in 2D layout editor for virtual metrology and analysis.

DRIE (Deep Reactive Ion Etching) has scalloping issues which need to be analyzed and controlled. To characterize the scalloping effect, comb fingers of the Tunable Capacitor were etched using SEMulator3D’s DRIE Custom Python module which provides anisotropic etching through a time-domain multiplexed processing scheme. In this scheme, etching and polymer deposition are alternated to pattern high aspect ratio of structures.

Above images show the SEM (Scanning Electron Microscope) view of fabricated and SEMulator3D view of simulated DRIE profile of inter-digitated comb fingers. The average values of parameters such as height, width and rate are highly dependent on design parameters and etching equipment. There is good agreement between the simulation and experimental results.

The image above shows a scallop dimension, simulated on SEMulator3D, of 501nm height and 176nm width. Longer etch cycle times are responsible for larger scallop heights that in turn are responsible for deeper scallops. A SEM view of similar fabricated etched parts compare well with the modeled view by SEMulator3D.

The Virtual Fabrication Platform of SEMulator3D accelerates the development time for MEMS devices by a large extent at significantly lesser cost and higher accuracy by eliminating in-fab set up and process variations during unit process interaction studies and quantitative analysis.

Alexandre Mehdaoui of Coventor has described in great detail the overall Virtual Fabrication process for MEMS with nice examples, pictures and references in his new whitepaperposted at Coventor website. It provides an interesting learning about what goes in fabrication and how that has been automated in a software tool like SEMulator3D.

More Articles by Pawan Fangaria…..

lang: en_US