IC place and route tools can be very high-priced EDA software to purchase or lease, so there’s some good news for AMS designers that need an affordable digital place and route tool for their mostly analog designs. Today the team at Tanner EDAannounced a totally new place and route system has been added to their Schematic Driven Layout (SDL)tool. I spoke with their CTO, Massimo Sivilotti on Friday to ask some questions.

SerDes: Four Wires Are Better Than Two

Kandou Bus SA has recently been proposing the technique ENRZ (Ensemble Non Return to Zero) for use as the next generation interconnect standard for the 56 Gb/s generation of interconnect interfaces at the OIF (Optical Interconnect Forum). ENRZ is technique where three bits are orthogonally modulated over four correlated wires. It delivers more throughput with lower power consumption than regular NRZ does. The receive eyes after ENRZ’s joint detectors are NRZ shaped and are compatible with off-the-shelf binary DFEs (Decision Feedback Equalizers).

ENRZ is also amenable to SerDes-like implementations that do not require DSP (Digital Signal Processing) and can be implemented as a “turbo mode” of two regular NRZ SerDes. ENRZ requires that the four wires be skew-matched to a similar constraint as the intra-pair skew constraint for differential pairs. An important channel for ENRZ is two loosely coupled differential pairs that are separated by a small gap. The ISI Inter-Symbol Interference performance of ENRZ is much better than that of PAM-4 (Pulse Amplitude Modulation 4-level).

At an OIF panel at OFC 2014 entitled “56 Gb/s Serial: Why, What, When?”, Brian Holden of Kandou Bus articulated the vision of using 4-wire ENRZ links in every portion of the system instead of using traditional differential links. He described how the 56 Gb/s generation that the industry is currently working is highly challenging because of the high baud rate. Beyond that, in the 112 Gb/s generation, there are almost no appealing two-wire alternatives. Because of these twin difficulties, a choice of a four-wire interconnect architecture in this generation can set the industry up for success in the both the 56 and 112 Gb/s generations.

Kandou presented a two generation interconnect architecture for electrical interfaces. That architecture is to use ENRZ at 37.3 GBaud over four wires for all of the interfaces of the 56 Gb/s generation. This interconnect delivers 112 Gb/s over four wires. A standardized bit multiplexing technique will be useful with any of the proposed 56 Gb/s interfaces including ENRZ, given the ubiquity of 25 Gb/s optical interfaces. There are several applications that have differing frequencies on each of the 28 Gb/s legs, notably Fibre Channel.

For the generation following, the ENRZ plus PAM-3 (Pulse Amplitude Modulation 3-level) can be used. That interface would run at 47.1 GBaud and would deliver 224 Gb/s over those same four wires. Neither PAM-4 nor PAM-8 are likely to be good choices for this interface due to their inferior ISI performance and PAM-4’s higher baud rate.

For both generations, the in-package, USR (Ultra Short Reach) interface has different constraints. Several good alternatives exist including 4, 6 and 8 wire alternatives.

Bottom line: a consistent four-wire interface is the optimal choice across the 56 Gb/s generation. Choosing this interface for the 56 Gb/s generation will also set the industry up to succeed in the 112 Gb/s generation. Four wires are better than two.

About Kandou Bus S.A.

Headquartered in Lausanne, Switzerland and founded in 2011, Kandou Bus is an innovative interface technology company specializing in the invention, design, license and implementation of unmatched chip-to-chip link solutions. Kandou’s Chord™ technology lowers power consumption and improves overall performance of semiconductors, unlocking new capabilities in electronic devices and systems. www.kandou.com.

More Articles by Daniel Nenni…..

lang: en_US

Dinner with Dr. Walden C. Rhines!

You are cordially invited to have dinner with my favorite EDA CEO, Dr. Walden C. Rhines (the C stands for Clark by the way). Wally will be the dinner keynote speaker at the Electronic Design Process Symposium on April 17[SUP]th[/SUP] at the Yacht Club in Monterey. When registering use Promo Code: SemiWikiGofor $50 off. Such a deal! Register HERE today and have dinner with Wally and 49 other semiconductor professionals you can add to your personal network.

Coincidentally, I was at Mentor HQ in Wilsonville last week and let me tell you I was very impressed. If not for the constant rain, I wouldn’t mind moving there myself. It is an absolutely beautiful campus with everything you would possibly need including a child development center. Given the average age of the EDA professional it is more likely a grandchild development center!

First was breakfast with Sonia Harrison. Sonia is not only a seasoned public relations professional, she is also a famous Jazz singer. If you did not hear her sing at #50DAC in Austin last year you can hear her this year at #51DAC in San Francisco. According to my beautiful wife (I’m tone deaf) Sonia has an amazing voice and sings on key so no auto-tune required!

My next meeting was with John Ferguson, Marketing Director for Calibre DRC. John and I go way back to the Avanti days and the Hercules DRC tool. If I remember correctly, Avanti bought ISSI and renamed the Veritech DRC tool Hercules. John joined Avanti right after that and was my DRC AE. John updated me on DRC, 3D stacking, and Silicon Photonics. We also exchanged kids-in-college stories.

Greg Aldrich was next, Greg is the Marketing Director for Mentor Silicon Test Solutions. Test is the unsung hero of EDA but as we move forward with driverless cars, which may be sooner than you think, your life may depend on Silicon Test, absolutely.

The Tessentproduct suite provides comprehensive silicon test and yield analysis solutions that address the challenges of manufacturing test, debug, and yield ramp for today’s SoCs. Built on the foundation of the best-in-class solutions for each test discipline, Tessent brings them together in a powerful test flow that ensures total chip coverage.

There are 28 silicon test and yield analysis whitepapers HERE and 44 videos HERE.Mentor has an automotive solutions site HERE:

Connected Engineering™ for the Automotive Industry:System design tools from Mentor Graphics help you control the increasing complexity of designing and manufacturing today’s vehicles. Be it a sports car or a long-haul truck, each new model, feature, option, and variant multiplies the number of components and configurations that must be designed, integrated, produced, and managed.

#51DAC also has an automotive track lead by a keynote from James Buczkowski, Henry Ford Technical Fellow, Ford Motor Company:

Automotive Systems and Software

Ever increasing feature content enabled by electronics and software and the associated complexity has made development of automotive electronics and software amongst the largest challenges for the automotive industry. Today, the functionality, efficiency, time-to-market, cost, quality, safety, and security of a new vehicle are determined more by embedded systems and software than by any other factor.

The Automotive Track is a new, unique forum addressing design automation and design methodologies to enable automotive designers and integrators to meet their unprecedented challenges.

I will be at this one for sure: Tutorial 3: Automotive Embedded Systems – A Quick Introduction and the Road Ahead

More Articles by Daniel Nenni…..

SEMulator3D 2014 – New Enhancements for Virtual Fabrication in the 3D IC Era

A Virtual Platform for any kind of design or manufacturing in any discipline of science or engineering (electrical, mechanical, aeronautics etc.) must be able to provide an accurate representation of an actual design/product in a fraction of time and cost it takes to build working prototypes. In the case of semiconductors at technology nodes below 20 nm with incredibly complex structures, one can imagine how difficult it would be to truly represent a model of the actual fabrication process. But considering the tremendous cost and time of in-fab build-and-test cycles leading up to the final fabrication, it’s much more efficient to have a Virtual Platform to validate process development for fabrication. Kudos to Coventor for coming up with such a platform.

Since last DAC, I have talked about this innovative Virtual Fabrication Platform of SEMulator3D offered by Coventor. It provides an excellent software environment to quickly build-and-test a semiconductor or MEMS manufacturing process. The platform is versatile enough to let the designer or process engineer experiment with any kind of process technology such as FinFET on Bulk, FinFET on SOI, FDSOI and so on, and evaluate their design for fabrication through ‘virtual’ build-and-test cycles at their desk, thus saving enormous time and cost over in-fab experiments. It has the added benefit of letting them decide about the actual foundry to use when they have a perfect design in hand to be manufactured.

I am delighted to see the kind of progress Coventor has made, in a few years, to keep up with the pace of technology advancement. Each new release of SEMulator3D has enhanced the platform further to provide the ultimate fab experience to the semiconductor design and manufacturing community. The latest version of the platform, released this week, is perhaps the most exciting yet, adding features that improve prediction and accuracy, provide faster performance, enhance the GUI for ease of use, and many other improvements. It’s understandable; many enhancements are based on the requests from their customers who are seeing the real value in this Virtual Fabrication Platform. A list of important enhancements in SEMulator3D 2014 is mentioned in the press release.

I am particularly impressed with some of the very powerful modeling features which have been added. The modeling of various Pattern Dependent Etch effects provides great power to model today’s advanced 3D technologies. Several forms of pattern dependence such as Aspect Ratio Dependent Etching (ARDE) and Pattern Density Loading (PDL) have been added in the Basic Etch as well as MultiEtch model. The modeling coefficients and material-dependent coefficients can be either specified directly by expert process engineers or computed automatically by SEMulator3D by entering some measurement points through a Calibration Wizard. Since these are the features for seriously involved process engineers or designers, there are options to turn them off to not overwhelm general users of the tool.

Dr. David M. Fried, CTO, Semiconductor at Coventor, in his blog has a nicely pictured pattern dependent etch process in a model for via calibration which shows different levels of etching for an isolated via, an array of small vias and a single large via. It’s a must watch live! Clearly, this shows process sensitivity to the design topography and parameters that provides even higher predictability with high degree of accuracy in the fabrication of the design.

Structure Search is another powerful feature which can quickly evaluate the entire 3D model for yield-limiting structural failures, such as locations of insufficient dielectric thickness and other violations. Some example images are shown above. In fact, it can provide new learning about the failures which were not anticipated. The violations are reported in textual file along with graphical error markers over the 3D model. This is a significant transformation over the time and effort consuming design rules (in spreadsheet) based checks. This, combined with other existing powerful features like Expeditor (with enhanced GUI for easier setup and execution of multi-dimensional DOEs) and Virtual Metrology, provides the user full control to examine process variation, margins, design sensitivity etc. in most efficient automated way at her desk without experimenting through the actual fab.

Another feature to name is Layout-Aware Rebuild that is very efficient in incremental builds. From pure performance perspective, multi-threading has been introduced in many automated software processes.

The SEMulator3D 2014 is a significant step forward towards accurate modeling of process-design interaction for advanced semiconductor process. It enables the highest level of predictability to ultimately provide high yielding reliable designs at much lower cost and reduced time.

More Articles by Pawan Fangaria…..

lang: en_US

MIPI IP segment to reach $100M? Yes, …

… in 2019. At that time, the total Interface IP market is expected to weight between $900 million and $1 billion. If we want to understand this IP market segment dynamics, we have to look at protocol based products like USB (from USB 1.0 defined in 1996 at 12 Mbit/s to USB 3.1 supporting 10 Gbps data rate) or PCI Express (from PCIe gen-1 defined in 2003 at 2.5 Gbps to the soon to be released PCIe gen-4 at 16 Gbps). Each of these segments represents a close to $100 million market today. MIPI adoption rate has been slow at the beginning in the mid-2000’s, but multiples specifications have been defined since then, creating a real emerging IP market in 2013, weighting as much as the PCIe IP market in 2006. Moreover, the explosion of smartphones shipments and the massive move toward everything “Mobile” has attracted the chip makers and multiplied the opportunities for the IP vendors to sale MIPI IP. Last, but certainly not least, the clear wireless and mobile IC leader, Qualcomm, is also the chip maker most supporting MIPI.

MIPI follows the trends in the Electronic industry: the massive move from parallel to serial interconnect, as illustrated by PCI Express replacing PCI, SATA replacing PATA, HDMI or DisplayPort replacing LVDS based interconnect to Display material (computer screen or HDTV) etc… Using similar technologies in Mobile Devices is a natural move, but a specific attention has been taken to power consumption. MIPI has been specifically designed for portable electronic devices, battery powered, and lowering the power consumption is a key feature.

In this survey, we have started to look at the MIPI use in the Mobile Handset segment and first derive a forecast in term of Integrated Circuits (IC) because we think that the more widely MIPI will be used in chips in production, the more stable and easier to manage the protocol will be. When more IC is in production means more efficient –and cheaper- test program, leading to a null or marginal impact on yield. More identical IC in production also means cheaper production cost and consequently a lower Average Selling Price (ASP). We forecast MIPI powered IC shipments to be in the 5 Billion in 2014, passing the 10 Billion IC in production in 2017. Such a virtuous cycle is expected to lead to a wider adoption for MIPI technology.

In fact, we consider that MIPI is integrated in the vast majority of the smartphones, at least through DSI and CSI-2 specification, but also through Universal Flash Storage (UFS) integrating UniPro, UFS and M-PHY, and, to a lower extend, with Low Latency Interface (LLI), DigRF, SSIC or M-PCIe. We also expect some of the featured phone designs to integrate DSI and/or CSI-2 and the high hand media tablet to integrate MIPI specification, as the smartphone Application Processor are commonly integrated into the tablet. We have seen that the smartphone and tablet sales explosion is nowadays coming from Asia, going with the emergence of multiple wireless start-up, these being good candidate for MIPI IP external sourcing, unlike the well-established historical players.

All of them selecting the technology to get full benefit, on top of the low power consumption, from MIPI usage:

- Standardized Interconnect protocol: an OEM can run seamless integration in the system of the different IC, providing they comply with the same MIPI Interfaces.

- Interchange suppliers at low risk: an OEM can easily move from one IC supplier to another for the same function (for example a camera controller IC), at least at the Interface level

- There are different specifications for the Controller (CSI, DSI, LLI and so on), but only two for the PHY (D-PHY and M-PHY): many specifications, but an easier learning curve to physically interface the application processor with Camera, Display, Modem, Mass Storage, WLAN, Remote Coprocessor…! In fact, we should say three, counting the soon to be released C-PHY specification, which is expected to replace D-PHY for the chip makers allergic to M-PHY…

In the survey we propose the 2010 to 2013 actual results by IP vendor, as well as a 2011 to 2020 forecast. This forecast has been made by market segment:

- Wireless handset

- PC and Media Tablet

- Consumer Electronic (CE), Industrial, Medical and IoT

We have also organized these data by MIPI IP type: PHY or Controller IP (see Table)

We provide license price indication, by technology for the PHY specifications. We also propose a review of the different IP vendors actively marketing MIPI PHY IP, or Controller IP or both. This competitive analysis could benefit to:

- MIPI new adopters, or the chip makers integrating MIPI in devices serving wireless handset segment (smartphone or not), Media Tablet and PC and Consumer Electronic segments,

- IP vendors, who desire to develop a new IP business or consolidating existing business and invest resources on line with MIPI IP business potential.

- VIP vendors who invest into this new source of business, after having supported USB, SATA, PCI Express…

This MIPI IP survey or one of the two previous versions has been sold to IP vendors (already supporting MIPI or in the decision process to support these specifications), VIP vendor and chip makers. This report is unique: it’s the only one where the reader can find both an IC and an IP forecast for MIPI, as well as a competitive analysis of the IP –and VIP- vendors. As such, if your company is or will be involved into MIPI, you need to have it.

Table of Content for “MIPI IP 2010-2013 Survey – Forecast 2011-2020” available here

From Eric Esteve from IPNEST

What is Next for GLOBALFOUNDRIES?

In response to changing industry dynamics, AMD announced in October 2008 a new strategy to focus exclusively on the design phase of semiconductor product development. To achieve that strategy, AMD partnered with Advanced Technology Investment Company (ATIC) of Abu Dhabi to create a new joint venture company designed to become the world’s first truly global contract manufacturer of semiconductors.

On March 4, 2009, GLOBALFOUNDRIES was launched as a new joint venture combining AMD’s leading-edge semiconductor manufacturing capabilities with the long-term financial backing of ATIC. This created a new global semiconductor manufacturing foundry with approximately 3,000 employees with AMD as its first customer.

In January 2010, the company announced the completion of its merger of operations with Chartered Semiconductor, a global semiconductor foundry based in Singapore. At the time, Chartered consisted of about 7,000 employees, mostly based at the company’s 6 fabs in Singapore.

Today, GLOBALFOUNDRIES is wholly owned by ATIC and is the world’s second largest independent semiconductor foundry. However, GF is still one fourth the size of number one foundry TSMC and faces stiff competition from the ever aggressive Samsung Foundry Division and the newly launched Intel Custom Foundry Business Unit. More recently, GF shuffled the executive staff and acquired a new CEO:

Santa Clara, Calif., January 6, 2014 —Building on the successful track record of its first five years in the semiconductor industry and its continued commitment to build out its global network of manufacturing facilities, GLOBALFOUNDRIES announced today, from its new offices in Silicon Valley, Sanjay Jha has been appointed as the company’s new Chief Executive Officer. Jha has served as CEO of Motorola Mobility Inc. and as the COO of Qualcomm Inc.

After spending 14 years at Qualcomm, Sanjay joined Motorola Mobility as CEO in 2008. Sanjay then sold Motorola Mobility to Google in 2011 for $12.5B with an exit package of more the $65M. Google then sold Motorola Mobility to Lenovo in 2014 for $2.91B. Yes Sanjay is a very clever man and he knows the fabless semiconductor ecosystem inside and out.

The $100B question is: What is next for GLOBALFOUNDRIES? The wild card here of course is Sanjay Jha. I do not know Sanjay personally (yet) but I do know people who know him and based on this, I’m wildly optimistic!

It is highly unlikely that Sanjay signed on to continue to stay the course at GLOBALFOUNDRIES. Being a second source or boutique foundry against the likes of TSMC, Samsung, and Intel makes no sense whatsoever. My guess is that Sanjay will go on an acquisition spree with the intention of building a major force in the semiconductor industry, absolutely. If I were Sanjay I would start with MediaTek and I will tell you why in the comments section. Acquiring the IBM semiconductor operations is also on the table I hear.

GF reads SemiWiki so offer your advice to Sanjay. This could be a real game changer, absolutely!

About GLOBALFOUNDRIES

GLOBALFOUNDRIES is the world’s first full-service semiconductor foundry with a truly global footprint. Launched in March 2009, the company has quickly achieved scale as the second largest foundry in the world, providing a unique combination of advanced technology and manufacturing to more than 160 customers. With operations in Singapore, Germany and the United States, GLOBALFOUNDRIES is the only foundry that offers the flexibility and security of manufacturing centers spanning three continents. The company’s three 300mm fabs and five 200mm fabs provide the full range of process technologies from mainstream to the leading edge. This global manufacturing footprint is supported by major facilities for research, development and design enablement located near hubs of semiconductor activity in the United States, Europe and Asia. GLOBALFOUNDRIES is owned by the Advanced Technology Investment Company (ATIC). For more information, visit http://www.globalfoundries.com.

More Articles by Daniel Nenni…..

lang: en_US

Xilinx and Red Pitaya is Tootie Fruity

Xilinx’s Zynq SoC is the best selling FPGA of all time. Zynq has brought together, at first an uncomfortable but necessary mix of software and hardware engineers. Two very different but special kind of people. Me, I’m of the hardware persuasion. Zynq is the start of the much needed open FPGA community. This will drive down the price of boards, increase quality and create vast amounts of free open resource, design, code and apps.

Last week a Red Pitaya board came in the mail for me. I was under the weather and had a long week of calls etc… so I get on our bed (sleep number bed, Hi I’m Luke and my sleep number setting is a 45. By the way, we engineers can make that thing so much better. I almost hacked it already but the wife gave me the ‘Look’), and started hooking up the Red Pitaya board. The Wife looks at me like ‘that is really romantic’. Now do not harp on me, I know all about romance for goodness sake, I have 7 kids, Cary Grant move over.

As I unpacked the Red Pitaya box, my wife curiously looked on, just waiting for some blinding LED to come on… Or even some smoke. 6 Years ago I burnt up our bed sheets with two 1940’s phones, 12V battery, wire and some R and C’s. They were my wife’s favorite sheets and my sons laughing on was no help. Dear reader, I feel like you are family so please keep these stories just between us.

The out of the box experience for Red Pitaya was off to a shaky start. It did not come with a power supply so I just grabbed my phone charger. Threw in the SD card, and crickets. No done lite. I downloaded the latest build and put on the SD card, and crickets. Lesson Alert here reader, not all USB phone chargers work, and I should have READ the instructions! 5V , 2A supply needed. I swapped it out for another and the brilliant blue done lite of success came on! I hooked up my USB COM port to my laptop, and a typical data stream.

The TeraTerm Screen was displaying all the usual CPU board goodies, more status you could shake a stick at. It even told me I was running a 20 out of 100 on the romantic scale, which is a new feature in Xilinx FPGAs called RomanticMon. You will not find that in Altera I assure you. Lesson Alert 2, my direct connection to my laptop Ethernet was no worky. I tried and read everything. Even though some users were able to do a direct connect to the PC, the documentation says you need to use a router. I did not care as I wanted to use Red Pitaya only for Wi-Fi connectivity anyways.

This is what I want from every FPGA board, I simply plugged in a USB Wi-Fi Dongle, changed a configuration file and my Droid was talking with the board, it was that easy! I can use my Droid over the 4g to control and status the board! This is the greatest feature of Red Pitaya and so far the best out of the box experience I had with any FPGA board. I’m using my Red Pitaya to start living the Internet of Things. I ran the spectrum analyzer on my phone and grabbed a RC remote from my kids. Hit the button and sure enough a nice 27 MHz signal with a small second harmonic 54 MHz showed up (See above).

Now is the board worth $299 of lab equipment? You can buy a better Scope for $299 but that will not get you the flexibility that the Red Pitaya gives you, not even close. You cannot do the list below with a Scope… Here a few ideas of what you can do with Red Pitaya:

- Audio solutions, adaptive noise cancelers

- Gun Shot detectors, Washington DC uses these already…

- Mini EW RADAR + PRI Tracker + Digital RF Memory + Technique generator

- 2 Channel Narrow Band RADAR

- Low Frequency/Narrow Band Software defined radio

- Medical networks, all patients in the hospital can be viewed by the doctor on the smart phone

If you want to keep the whole design in C/C++ I highly recommend Xilinx’s Vivado HLS. I really love the Red Pitaya! Great start for the Red Pitaya team and I look forward to growth, new apps, and versions of the board. Keep up the great work and for goodness sake put a reset button on this thing… It may add 1 cent to the budget but I think it is really worth it. Some business would spend $100k on a trade study for that…

lang: en_US

Semiconductor IP Validation Gets Faster

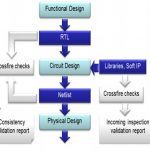

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort. Another approach is to automate the process of IP validation, and you could start to write your own scripts and create your own IP validation system after spending many man-years of effort. There is a faster way to validate IP and that is to consider using EDA software from a company that has specialized in this area, and that company is Fractal Technologieswho offers a tool called Crossfire.

IP Validation Flow using Crossfire

Out of the box Crossfire already performs over 150 validation checks on your logical and physical IP file and database formats, but what if you needed to create your own customized checks? Newly added is the ability for you to code your own checks called a Crossfire setup by using an API (Application Procedural Interface). Most EDA companies offer you an API in only one language, however Fractal was quite accommodating by providing their new API in three languages: Python, Perl and TCL.

Here are some applications for writing user specified checks:

- Logical Design Checks

- Check for busses when they may not be used

- Check for your own bus naming conventions

- IC Layout Checks

- Checking the area of a cell

- Is the boundary layer on a correct grid

- Does the boundary match the cell statements for dimensions and origin

- Checking for half design rule distance at the boundary of a cell

- Is the boundary layer on the top-level

- Is the text hierarchy placed correctly

So, whether you simply use the built-in library validation checks with Crossfire, or add your own checks, the end result is that your latest SoC has a higher verification confidence level so that you can sleep better at night and improve your chances of first silicon success.

Redesigned Web Site

If you haven’t visited their web site in a while, then consider browsing their newly re-designed site. I found it much easier to navigate and find the info I was looking for. Their new header is a bit hypnotic as it gradually changes colors like a chameleon.

ChipEx and DAC

For our IC designers in Israel, you can visit the Fractal engineers at the ChipEx 2014conference from April 29-30 in Tel Aviv. Then in June 2-4 you can visit booth 507at the DACconference in San Francisco. I visited their booth at DAC last year and blogged about it here.

Further Reading

- Correct by Construction Semiconductor IP

- Semiconductor IP Library QA Just Got Easier

- Validating Hard IP & Std Cell Libraries at DAC

- Quality in Design Formats has become a must!

- Do my tests certify the quality of my products?

- Is my Library or Semi IP really OK to use?

- Crossfire – Builds Quality with Design

lang: en_US

A Brief History of Mobiveil

Semiconductor IP is a relatively established frontier for innovation in Silicon Valley but it is not as easy as it looks. It certainly is not as easy as the two year old start-up Mobiveil has made it look. With a team of more than 100, led by experienced Semiconductor IP professionals, Mobiveil already has a portfolio of silicon proven IP (PCI Express, NVM Express, Serial Rapid IO, DDR4/3, Flash controllers, SPI4.2, 1G and 10G Ethernet) and high profile customers around the world (Samsung, LSI Logic, CSR, IXIA, Sanmina, Silicon Motion, Altera, and Marvel Semiconductor among others). The question you probably have is: Just how did they do it?

If you look at the Semiconductor IP usage trends over the last ten years the number of unique IP per tape-out is increasing while the ability to re-use IP across nodes is dropping. The top fabless semiconductor company IP groups will also be stretched thin supporting multiple fabs and complying with stricter security restrictions on the new FinFET process nodes.

Today, interface IP is dominated by large EDA companies including Synopsys and Cadence, both multi -billion dollar organizations. To successfully compete against large brute force companies, a start-up must be agile and aggressively push the technology while providing superior services, customer support, and leveraging joint development agreements whenever possible.

According to an article in Silicon India last month: Mobiveil started with founding executives and core engineering teams who have worked together for the last decade. The team understands a constantly evolving market, customers, competitors and partners. According to CEO Ravi Thummarukudy, the team’s strength lies in complementary skills and capabilities and a common vision and culture forged over ten years of working together at their previous startup, GDA Technologies, Inc., (GDA). While Thummarukudy brings over twenty five years of experience in semiconductor IP and electronic design automation, Gopa Periyadan supplies business development skills honed managing large sales operations. Technologist Amit Saxena’s contribution is over ten years developing semiconductor IP that has seen successful production in millions of devices. Managing Director of India operations, Srinivasan Durai brings the engineering leadership and India’s talented technology workforce to the company. The team has worked cohesively through the up markets of 1998-2000, 2005-2007 and the down markets of 2001-2003 and 2008-2009. This solid foundation brings unique strength to Mobiveil.

The other critical piece of the semiconductor IP start-up puzzle is sales. I cannot stress more the importance of hiring an experience sales executive early in the development cycle. Mobiveil executed perfectly by hiring LSI, Denali & Cadence IP Sales Veteran, Dale Olstinske (Denali was purchased by Cadence for $315M in 2010). I competed against Dale while working at Virage Logic and can tell you he is one of the top IP sales executives, absolutely.

You can read more here: Mobiveil: Riding the Rapidly Emerging Silicon IP Wave

About Mobiveil, Inc.

Mobiveil is a fast‐growing technology company that specializes in development of SIP, platforms and solutions for the networking, storage and enterprise markets. Mobiveil team leverages decades of experience in delivering high‐quality, production‐proven, high speed serial interconnect SIP cores and custom and standard form factor hardware boards to leading customers worldwide. With a highly motivated engineering team, dedicated integration support, flexible business models, strong industry presence through strategic alliances and key partnerships, Mobiveil solutions have added tremendous value to the customers in executing their product goals within budget and on time.

Mobiveil is headquartered in the Silicon Valley with engineering development centers located in Milpitas, CA, Chennai and Bangalore, India, and sales offices and representatives located in US, Europe, Israel, Japan, Taiwan and People Republic of China. For more information, please visit http://www.mobiveil.com

More Articles by Daniel Nenni…..

lang: en_US

FinFET Custom Design

At CDNLive, Bob Mullen of TSMC gave a presentation on their new custom FinFET flow, doing design, and verifying designs. At 16nm there are all sorts of relatively new verification problems such as layout dependent effects (LDE) and voltage dependent design rules. We had some of this at 20nm but like most things in semiconductor, it gets harder with each process generation. I’m going to leave verification until another blog.

He wasn’t talking about digital SoC design, which broadly speaking is the same as before. You write RTL, synthesize the design, place and route it and then run verification. Mostly the tools take care of the hard stuff like double patterning. And whoever designed the standard cell libraries took care of all the complicated FinFET stuff. He was talking about custom and analog design where you do actual transistor level layout.

I’m sure you know what a FinFET transistor looks like these days. What you may be less aware of is that they have to be laid out in a sort of matrix. The fin is a fixed size and so the only thing you get to vary about a transistor is how many FinFETs you get to join up in parallel to build a wider transistor. This is often referred to as quantization. In planar devices we used to be able to vary the width and length how we wanted. Actually by the time we got to 20nm this wasn’t really true, the design rules were so restrictive that the transistors were also pretty much laid out in a matrix. To build them, for lithography reasons, the gate material needed to be laid out in parallel lines at the appropriate spacing and then a cut-mask used to split the gate lines up into transistors. So the length of the transistors was pretty much fixed but at least we got to pick the width. With FinFETs we used the same technique but we don’t get to pick the width arbitrarily, just how many fins are controlled by the same signal. So a FinFET design consists of rows of source/drain with rows of gate running orthogonally.

Above is a very simple representation. TSMC doesn’t let anyone see their layout except under NDA so this is actually Cadence’s generic FinFET process used for testing tools early in the whole process. And the planar transistor on the left is nothing like the last planar process at 20nm, it is more like how things looked at 90nm when lithography OPC constraints were a lot more forgiving.

On the right is a FinFET inverter. First thing to note is that the inverter seems to have three gates (red), which is true. Every transistor has to be terminated with dummy gates on either side. You can’t just cut off the diffusion by just ending the polygon like in the planar device on the left. You need to tie it off with a gate. This was actually true at 20nm too, which is one reason I said that the planar transistor was from an old process node. In the middle you can see the red hashed area, that is the cut mask that separates the P and N transistors.

The first thing TSMC did was build a capability into the PDK to build a “transistor” that took as input how many fins were to be used. It created the layout, including dummy gates and well boundaries.

Then they created a schematic migration methodology to automate much of the migration of designs from 20nm by picking appropriate fin-counts close to simply scaling a planar transistor to 16nm. The voltages are different, the PDKs are different, and the quantized nature of FinFETs needed to be taken into account. But when they were done they would have migrated:

- Circuit symbols and schematics

- Hierarchical design configuration view

- Electrical & Physical design constraints

- Functional behavioral modeling views

- Testbench schematics and setups

However there is still no layout and the schematic is almost certainly going to need to be changed before the cell is finalized. The first step is thus to circuit simulate the schematic using estimated parasitics to get a starting point for getting to a layout.

The next step is rapid analog prototyping, to iterate between layout, extraction, circuit simulation and tweaking transistor sizes and layout constraints. The actual layout is automatically generated under the constraints. Every time the layout changes the parasitics change so hopefully the process converges reasonably fast.

Then onto verification. But that is a topic for another day.

If you have a Cadence account you should be able to find Bob’s CDNLive presentation here.