One of the most interesting demos at #51DAC was the eSilicon GDS II online quote system for TSMC. Probably because eSilicon was one of the most interesting companies exhibiting this year. While writing the book “Fabless: The Transformation of the Semiconductor Industry” we took a close look at the history of fabless semiconductor design. An instrumental part of that history was the ASIC business model where design teams big and small could toss a design spec and a big wad of cash over a wall and get a chip manufactured. eSilicon transformed the ASIC business model by creating a success based partnership with customers that has resulted in hundreds of designs that may have never been.

Also Read: We Need One MILLION Design Starts!

The next transformation you will see is what I call putting the “e” back in eSilicon by internet enabling semiconductor manufacturing. Paul McLellan wrote about it recently: Online MPW Quote Systemand GDS II Online for TSMC. The goal here is to enable design starts and get them into production as quickly and as error free as possible. This is the perfect vehicle for IoT designs, absolutely!

eSilicon’s online quote system for multi-project wafer (MPW) shuttle services delivers instant, executable quotes. The service is accessed through user-friendly web or smartphone interfaces allowing users to evaluate the wafer cost of multiple options in real time at no cost or obligation.

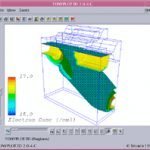

eSilicon’s GDSII portal offers the ability to fully specify the manufacturing process requirements for submission of a GDSII design to TSMC for manufacturing. The required manufacturing process information is specified through a series of easy-to-use menus, along with requirements for packaging, testing and delivery. An executable quotation from eSilicon is provided that includes non-recurring engineering (NRE) pricing and unit pricing for the system-on-chip (SoC) device.

Calling all IoT entrepenuers!

Next month SemiWiki and eSilicon will be doing a webinar on the GDS II portal. I hope to see you there:

GDSII online quoting webinar overview

Choosing all the options necessary to tape out a completed GDSII design for volume manufacturing can be a daunting task. Which process node, what process options, which package and what tester to use are just some of the important questions to answer. And there are many optional services to consider as well. It can take several weeks to months to collect all the information to create a single, complete quotation.

What if you could go to one place and browse all the options available, then generate a complete, executable quotation in minutes? Thanks to eSilicon and TSMC, it is now possible to do just that for a wide variety of TSMC technologies.

What you will see

In this informative, interactive webinar you will witness an actual quote being generated based on real designer input. You will be taken through all the steps required to generate a complete, executable quotation that addresses tapeout costs, optional services and volume production pricing for a new chip design. And we’ll do it all in about 10 minutes using the automated GDSII quoting tool.

We’ll also take you on a journey of discovery, highlighting how various options can be traded off and how those trade-offs impact the final quotation. If you plan to tape out a design for volume manufacturing, you must attend this webinar.

More Articles by Daniel Nenni…..

eSilicon, a leading independent semiconductor design and manufacturing solutions provider, delivers custom ICs and custom IP to OEMs, independent device manufacturers (IDMs), fabless semiconductor companies (FSCs) and wafer foundries through a fast, flexible, lower-risk, automated path to volume production. eSilicon serves a wide variety of markets including communications, computing, consumer, industrial and medical. www.esilicon.com.

lang: en_US