There are many facets of our lives that are being driven to a more virtual method of doing things. This is largely due to issues such as scaling due to whatever reason – technical, business, economic. Let’s look at some general cases: In yesteryears people used to travel all the way for face-to-face meetings; today virtual meetings using video conferencing technology happen within couple of clicks on your Smartphone or notebook. Similarly, I completed one of my management courses attending only virtual classes throughout the course on my notebook screen for several months. And people from across the world often attend on-line webinars on important technical topics. These are just a few ways we see technology enabling more efficiency by moving from physical to virtual, saving us significant time and costs. And these virtual solutions are proven to work very well.

These are mainstream examples but we can see the same trends in the semiconductor area which is growing more and more complex by the day as we move towards newer nodes. The design of a chip is by its nature a virtual process driven by EDA tools. The latest examples being virtual prototyping and virtual platform for architecting and optimizing an SoC at the system level. A chip design sees the real world only at the time of fabrication in a foundry, which tells about how close was the design to the reality. This is a very simplistic visualization of this scenario.

Things get really complex and murky when we look at process variation taking place at ultra low nodes. The result then is what you design is not what you get in the actual fab and you end up in several cycles between the design and the fab. In such a situation, the idea of a Virtual Fabrication Platform to quickly experiment, measure process sensitivities and devise process integration steps for the designs to work correctly during actual fabrication proves to be a boon. It saves time and costs for process engineers and design engineers.

I can recall about a blog I had written about a year ago about how 3D NAND Flash development can be accelerated with the use of Virtual Fabrication, in which David Fried, CTO – Semiconductor at Coventorhad provided his great insight into Virtual Fabrication and how SEMulator3D can help.

Read to know more – What Can Accelerate 3D Semiconductor Manufacturing

Today, while reading an articlewritten by Ryan Patz of Applied Materials who earlier worked at Coventor as well, it revived my memories about the business and technical crisis NAND Flash is experiencing. While 3D NAND is still away, 2D NAND needs continuous scaling in order to be profitable for business. And that needs extensive experimentation to build newer process models for smaller feature sizes and higher yields.

Ryan is a known expert in semiconductor fabrication technology. He studied the quadruple spacer patterning technology, slimming of floating gate (FG), and word-line (WL) and bit-line (BL) direction air gap to enable a “Middle-1X nm NAND” (M1X-NAND) flash memory cell announced by SK Hynixat last year’s IEDM 2013 and experimented further on SEMulator3D’s Virtual Fabrication platform to build a process model to understand the bidirectional air gap formation and corresponding process sensitivity because it’s necessary for the ‘quadruple spacer technology’ to overcome the effects of process variation to deliver a narrow distribution of device performance.

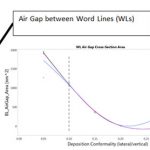

The air gap formation in both directions, WL and BL, is extremely sensitive to the conformality of the dielectric deposition process and FG slimming. In the above image, the baseline model is seen to be centered right in the middle of a steep sensitivity with deposition conformality (lateral/vertical) ratio of 0.1. Any small variation in deposition conformality can have large impact on the air gap cross-section area.

This study clearly shows the advantages of process studies in a virtual platform which can be quickly done off fab and used for process optimization and prioritization. The SEMulator3D is quite well-equipped to devise new optimized process integration flows for the newest nodes and help scaling future technologies.

I am happy to see this study done by using SEMulator3D to further prove the power of Virtual Fabrication. Read Ryan’s article to know more about this study here.