The semiconductor industry has never been more exciting than it is today, at least not in my 30 years of experience. Things are moving faster than ever before making collaboration at all levels a requirement. At SemiWiki we are afforded the privilege of passes to semiconductor conferences around the world. We also have access to all levels of the fabless semiconductor ecosystem and speak with people both on the record and off. Even so, some of the best information comes from forum discussions, absolutely.

When we first started SemiWiki it was really meant to be a forum with wikis and a place for my weekly Silicon Valley Blog. Fortunately industry experts Paul McLellan and Daniel Payne agreed to move their blogs from EDN to SemiWiki and the rest is history. We now have eight industry experts on staff and dozens of others who blog when they have something of semiconductor interest to say.

The forums however are a different form of communication and a very important one. As you can see we have expanded our forum section to include additional subject areas:

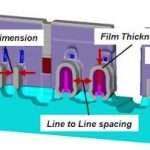

Semiconductor Process Technology

TSMC, Intel, Samsung, GF, UMC, SMIC, 28nm, 20nm, 16nm, 20nm, 10nm, etc…

Electronic Design Automation (EDA) Software

Cadence, Synopsys, Mentor, Ansys, Atrenta SpyGlass,, Calypto, Carbon Design, ClioSoft, Coventor, Dassault, Fractal Technologies, Methodics, MunEDA, Silvaco, Tanner EDA, Etc…

Discussions on the latest SoCs and related technologies

CPU, GPU, LTE, 4G, etc…

Semiconductor IP Market Place Threads

A place to share your IP! DSP, PCIe, USB, DDR, MIPI, HDMI, NoC, etc…

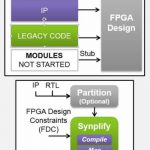

Programmable Devices

Discussions on FPGA, PLD, and CPLD technology, design, and implementation, Xilinx , Altera, Lattice, and Cypress.

Microcontrollers

Discussions on embedded technology, design, and implementation

ARM, Analog Devices, Atmel, Freescale, Infineon, Intel, Maxim, Microchip, NXP, Renesas, Silicon Labs, STMicro, TI, Zilog

Mobile Devices

Discussions and product reviews for smartphones and wearables. Post a review of your favorite mobile gadget and lets crowdsource!

Internet of Things (IoT)

Discussions on IoT and Security. SemiWiki is staffed with IoT experts so this is the place to ask questions, absolutely!

Digital Fabrication: 3D Printing, CNC Milling, Laser cutting, etc…

Discussions and meet-ups on the latest technologies for digital prototyping.

Semiconductor Related Stocks

Where investors and semiconductor professionals interact. Please put stock ticker in subject of all posts: INTC, TSM, QCOM, ARMH, ALTR, XLNX, SNPS, CDNS, MNTR, Etc…

Semiconductor Related Jobs Forum

This is an open forum for recruiters and job seekers. Post jobs here for free! For the greater good of the semiconductor industry!

Each forum will have moderators so if you see one you are passionate about and would like to be actively involved let me know. There is fame but no fortune unless you consider the knowledge and relationships you will gain which is truly priceless. You will have direct connections to hundreds if not thousands of semiconductor professionals in your area of interest. Just imagine the possibilities!

As I mentioned in my blog “EDA Tool Reviews” we want honest and unfiltered opinions, observations, and experiences with tools and technology for the greater good of the fabless semiconductor ecosystem. The same goes for the other forums. Start discussions, ask questions, share your semiconductor design successes and failures so we all can all learn from them. Be an active part of the crowd that changed the world because our work is not done.

It is easy to get started, just register for SemiWiki (use your real name or not) and pick the forums that interest you. While you are in the forum just click on the Forum Tools tab and subscribe so you get notified whenever there is a new post. Or you can subscribe to the RSS feed, simple as that.