Driving into DAC on Sunday afternoon was a chore since Gay Pride week was finishing with the Gay Pride Parade. Streets were closed, traffic was crazy, and people were roller skating naked which seems wrong on so many levels. This year the opening ceremonies were in the convention center hallway which also seemed wrong. Long lines for food and drink and a small flat screen for the presentation but thankfully no naked roller skaters.

Richard Valera from Needham kicked things off with an EDA overview from the financial side. This is the slot Gary Smith EDA previously occupied. Rich has an EE degree from Carnegie Mellon and spent his first few years in EDA with Racal Redac, Viewlogic, and Synopsys. He then got an MBA/Finance degree from Rutgers and has been at Needham covering technology, including EDA, for the past 20 years. Rich and I are like minds in regards to EDA, absolutely.

Rich went through 20 slides (attached) but it was a bit hard to hear and see so he sent me the slides and we chatted afterwards.

- What’s driving EDA growth?

- What’s the growth rate of EDA been doing?

- EDA IPO’s/Consolidation

- Private and public investment in the EDA industry

- Conclusions

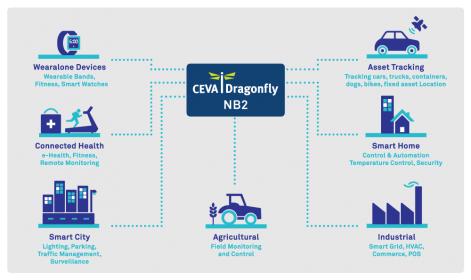

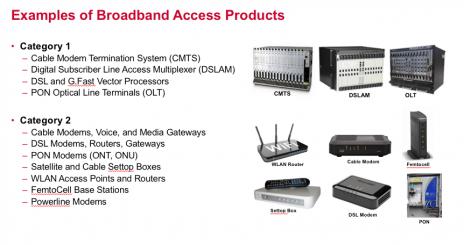

Automotive, IoT, AI/ML, and the Cloud are driving EDA of course. We see this on SemiWiki in the categories we track and the domains that visit us. One concern I have, and Rich shares this concern, is that we are experiencing a bubble of design activity especially with Automotive and AI. The last time I talked to Wally Rhines about automotive he compared today’s automotive burst to the one in the early 1900s where there were 285 car companies that narrowed down to 3 and now we are back up to more than 300 car companies suggesting history will repeat itself sooner than later. My bet is much sooner, as in the next 3-5 years.

At a DAC fireside chat Wally reiterated that VC money is back for semiconductor start-ups and the semiconductor industry will continue to grow. More than $900M was invested in 2017 with AI playing a role in the majority if not all of them. Deja vu of the dot com bubble maybe? Successful or not, they all have to buy EDA tools thus the rosy EDA outlook.

Rich discussed the FAANGs (Facebook, Apple, Amazon, Netflix, and Google) which was a new term to me. Amazon, Google, and Facebook are definitely upping their design activity. We see this on SemiWiki. Mostly, in my opinion, it is IP driven traffic with companies doing the “make versus buy” analysis. Our IP readership has always been a strong source of traffic and even more so today. Thus far we have published 761 IP related blogs that have been viewed 3,967,058 times by 26,852 different domains.

Bottom line: Just about everyone on SemiWiki reads about IP, absolutely.

Rich also talked about EDA investment and consolidation. We have a front row seat to this horror show as well. With the Siemens acquisition of Mentor, M&A has heated up a bit. It really is a battle between Synopsys and Mentor with Mentor having the bigger checkbook. SemiWiki has the most complete EDA M&A wiki HERE which was just updated with the Mentor acquisition of Austemper. EDA really is all about M&A and Mentor has the advantage today for the first time in many many years.

Rich then goes into EDA valuations which have risen nicely over the past few years. The reason really is simple and was very clear at the DAC exhibit hall. EDA is now three very dominant companies and a handful of smaller companies caught in between. The SNPS stock price has more than doubled in the past five years and CDNS has more than tripled. The big three EDA companies can now pretty much do whatever they want, they can even skip DAC next year apparently (Synopsys).

Rich’s summary slide:

- The EDA/Semi IP market is seeing healthy growth, with strength from Auto, IoT, A.I. and relatively new consumers of EDA in the webscale/cloud space.

- EDA has seen considerable consolidation, which has not been matched by private company formation and IPOs.

- VC investment has been limited due to smaller TAM size and long gestation of many EDA companies, but opportunities still exist for privates solving challenging problems.

- Overall (public and private) investment, revenue growth and job growth in the EDA/IP industry remain healthy.

- And public company investors have shown an increasing appreciation for the value of EDA, as reflected in higher absolute and relative multiples of public EDA companies.

Rich’s presentation is definitely worth a look (attached):