Sean Park is a seasoned executive with over 25 years of experience in the semiconductors, wireless, and networking market. Throughout his career, Sean has held several leadership positions at prominent technology companies, including IDT, TeraSquare, and Marvell Semiconductor. As the CEO, CTO, and Founder at TeraSquare, Sean was responsible for leading the company’s strategic direction and overseeing its day-to-day operations. He also served as a Director at Marvell, where he provided invaluable guidance and expertise to help the company achieve its goals. He holds a Ph.D. in Electrical Engineering from the University of Washington and also attended Seoul National University.

Tell us about your company?

Founded in 2016, Point2 Technology designs and manufactures ultra-low power, low-latency, and scalable interconnect mixed-signal SoC solutions. Headquartered in San Jose, California, Point2 is bringing interconnect technology to extend the reach of copper cabling and introducing an innovative technology to the market – e-Tube – that better addresses the terabit network bandwidth requirements inside the next-generation Artificial Intelligence (AI) / Machine Learning (ML) datacenters.

What problems are you solving?

Today’s datacenters rely on 400 gigabit (400G) Ethernet network devices that are transitioning to 800G. Point2’s UltraWireTM Smart Retimers are purposed-built for active electrical cables (AECs) to extend the copper cable reach required for in-rack and adjacent rack applications. AECs built with Point2’s UltraWireTM Smart Retimers consumes 40% less power and are 75% lower in latency. As AI/ML applications drive datacenters to 1.6T speeds and beyond, yesterday’s copper and optical interconnects, cannot scale to the future terabit requirements. Typically, optical technologies offer the speed and the bandwidth required but are expensive and power-hungry with temperature variability and reliability issues. Copper, the most cost-effective option, experiences significant signal loss at higher speeds with limited cable reach. Finding the optimal solution to overcome the limitations of these two technologies – scalable bandwidth, low power consumption, low latency, and at comparable cost to copper – is a daunting challenge for the datacenters. e-Tube is the answer.

What is e-Tube?

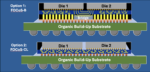

e-Tube is a scalable interconnect technology platform using RF data transmission through a plastic dielectric waveguide made of common plastic material, such as Low-Density Polyethylene (LDPE). Active RF cables (ARCs) built with e-Tube technology provides the ultra-low latency, energy-efficient, interconnect solution that is ideal for top-of-rack (ToR) to Smart NIC, ToR to ToR, and accelerator-to-accelerator connectivity in AI/ML data centers. e-Tube eliminates the fundamental limitations of copper at terabit speeds by supporting up to 7m cable reach with 50% of the cable bulk and 20% of the weight at a similar cost structure. Compared to optical cabling, e-Tube consumes 50% less power, with latency that is three orders in magnitude lower, at 50% lower in cost, and without temperature variability and reliability issues. This scalable technology is the ideal replacement for copper cabling for AI/ML in-rack and adjacent-rack applications.

What application areas are your strongest?

Point2’s expertise is in mixed-signal interconnect SoC designs with the lowest power and latency. Starting with our UltraWireTM Smart Retimers for 400G and 800G AECs that typically consume 40% less power and 75% less latency compared to other DSP-based Retimer solutions. Our cable partners have used these advantages to design and deploy AECs with hyperscalers and enterprises for switch-to-server and accelerator-to-accelerator connectivity for in-rack and adjacent-rack connectivity. With AI/ML data centers transitioning to terabit speeds, development for 1.6T and 3.2T ARCs is underway to address future AI/ML workloads. e-Tube technology is also expected to expand into ‘inside the box’ for chip-to-front panel and backplane applications with tighter integration with accelerator and switch ASIC manufacturers. This approach will deliver the higher interconnect bandwidth and port density required to keep up with future AI/ML accelerator speeds.

What keeps your customers up at night?

Over the next few years, AI/ML data centers must overcome three challenges simultaneously: 1) deliver better performance to meet soaring bandwidth demand; 2) contain costs while expanding in performance and complexity; 3) continue improving energy efficiency. It is this trifecta of challenges that keeps network operators up at night.

What is next for Point2 and the development of e-Tube?

The most important interconnect attributes are scalability, energy efficiency, low latency, and affordability. As the AI/ML workload evolves rapidly—pushing the limits on data rates with trillions of calculations being processed every second—it is vitally crucial that cabling interconnects support this rapid growth. Network requirements of 1.6T and 3.2T are approaching fast, and the industry must have the proper infrastructure to meet this demand while seamlessly adapting to new data rates. Our commitment is to continue to develop innovative interconnects that scale at the pace of the AI accelerators while achieving best-in-class energy efficiency and affordability required for mass deployment for the next-generation AI/ML datacenters.

Also Read:

CEO Interview: Nikhil Balram of Mojo Vision