A High-Definition Multimedia Interface (HDMI) IP core was being implemented in an advanced process technology. This fairly large and complex analog mixed-signal (AMS) IP comprising over 130K devices was close to being finalized and shipped to the customer. But many design rules at the foundry were unexpectedly changed from recommended to compulsory, creating hundreds of thousands of violations. It would have taken months to fix all the problems. An automated migration was really the only possible solution.

The main changes: New PDKs were received from the foundry incorporating modified PCells, changed rules for DRC (design rule check) and DFM (design for manufacturing). Some of the most significant were:

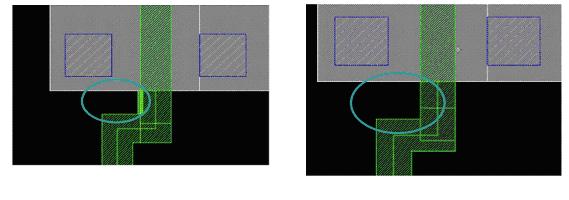

- Larger poly gate end-cap. Simple to fix when there is room for the extra poly but very hard to fix when there are other nearby transistors, poly etc

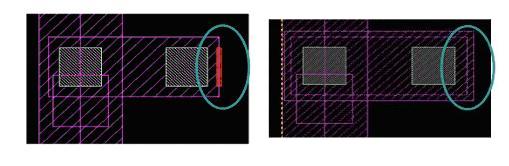

- Larger metal on via enclosure. Simple to fix if the via is isolated but very hard to fix in the typical case where the via is surrounded by minimum spacing routing

- Small notches prohibited

The main non-changes: Obviously the migration needed to be performed with minimal possible changes to the design, especially for an AMS block. In particular, design hierarchy needed to be maintained with no changes, and LVS must continue to pass. Corrections should have minimum affect on the design, especially in areas where no violations needed fixing. Virtuoso database integrity should be maintained, in particular structure, connectivity, Pcells etc.

The schedule: The runtime should only be a few hours to allow rapid iteration. At least 90% of the design rule and DFM violations should be fixed automatically. The entire project, including any manual fixup, and technology file creation, should be completed in 3 weeks.

How the above challenges were addressed:

Metal enclosure of vias bigger in target:meta1 enclosure around via needs to be enlarged without creating DRC errors due to the introduced extra metal. A similar change is required on all metal levels. The migration engine not only enlarges the metal enclosure, but will move adjacent wires where needed to maintain a correct spacing.

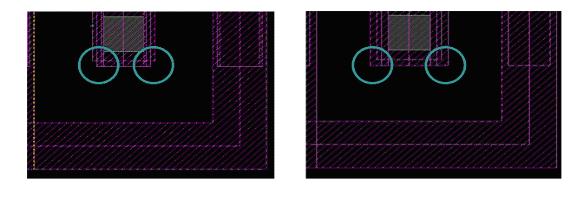

Replacing some Pcells introduced jogs: replacing some pcells and via cells with target PDK cells resulted in small metal jog DRC errors which needed to be removed automatically.

The poly to diffusion spacing was too small: at 90° gate connections the poly spacing to the source/drain diffusion needed to be enlarged automatically to be DRC correct. The migration engine will move adjacent poly wires or devices where needed to maintain correct spacing.

Experience : The Sagantec application engineer took about a week to set up the technology file from scratch and debug it, running a few sub-blocks to pipe-clean the flow and ensure that the results maintained LVS connectivity and Virtuoso database integrity. Mid way through the project, a still-newer PDK was received from the foundry with modified devices that required changes to the source layout database. However, due to having the automated flow in-place these changes caused only minimal delay compared to using massive layout resources to make the changes by hand.

The Sagantec tool automatically corrected over 95% of the ~250,000 violations created by the rule changes, both the DRC and the DFM problems. The remaining violations were easily handled and were cleaned up manually in less than a week of effort.

The final migrated design completely maintained the hierarchy of the original design and was LVS clean.

Results : The corrected output was available before the agreed deadline. Each iteration of the design took only a few hours to run. Over 95% of the violations were fixed automatically and the remaining ones were easily fixed within a week.

One big advantage of the flow was risk-reduction and change-management since rules, requirements and libraries were all unstable. The final Virtuoso database had exactly the same structure as the original layout and nothing in the database was lost or changed during the correction.

IP block Adaption: Altering a complex custom physical design IP to take account of design rule changes can either be done by an experienced and highly effective layout team or using an automated flow that handles almost all of the work automatically. But when the volume of modification is high and the schedule is tight, the manual correction route is no longer a viable option. Furthermore, with any subsequent changes of design rules, the manual work needs to be repeated, resulting in additional delays and cost. That is where automatic solutions, such as Sagantec’s migration technology, provide the most significant advantage, as once the flow is setup, rule update iterations can be completed in hours rather than weeks. In this case, layout adjustment work that would have taken 20 weeks was reduced to one week, effectively a 20x effort reduction. In addition to licensing the migration software, Sagantec also offers migration as a service, performed by its experienced application engineers. Such service offering minimizes the turn-around time, ensures optimal use of the software and accomplishes high quality results in the shortest time.

Sagantec Demo Suite Registration

*Note: to read/write comments you must log in.

Share this post via:

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry