Yes, verification technologies are open to innovation for improved productivity and performance in the face of ever growing SoC/IP design sizes and complexities. There is not much scope left in processor speed to improve, other than multi-core processors in servers which again need software properly architected to be thread-able… Read More

Tag: vip

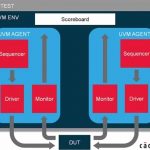

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More

Eric Esteve to Present during CDN Live 2014 in Munich

I will have the privilege to give an “IP Outlook” presentation during next Cadence event in Europe, CDN-Live to be held in Munich the 19[SUP]th[/SUP] to 21[SUP]st[/SUP] of May. I had a look at the agenda, and the conference will be pretty busy, especially on Tuesday, as there will be more than fifty presentations, starting at 10:30… Read More

Effective Verification Coverage through UVM & MDV

In the current semiconductor design landscape, the design size and complexity of SoCs has grown to large extent with stable tools and technologies that can take care of integrating several IPs together. With that mammoth growth in designs, verification flows are evolving continuously to tackle the verification challenges … Read More

$1 Billion IP & VIP sales by 2017?

We are not talking about ARM Ltd., as the IP vendor has already passed the $1B sales in 2013. In fact, we are not talking about a single IP vendor; this $1B mark will be passed by two IP market segments: Interface and Verification IP. In fact these two segments are very close together. When an IP is developed to support a specific Interface… Read More

Cadence Grows VIP Business – What’s New?

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

Happy Birthday to Synopsys VIP

I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More

Achieving Rapid Verification Convergence of ARM® AMBA® 4 ACE™ Designs using Discovery™ Verification IP

Synopsys is consolidating the company positioning on Verification IP. We have announced the launch of Discovery VIP in Semiwiki, in February this year, and we have commented about the acquisition of nSys and ExpertIO in January. This webinar, “Achieving Rapid Verification Convergence of ARM® AMBA® 4 ACE™ Designs using Discovery™… Read More

NVM Express: pervasion of PCI Express in SSD based storage

The verification IP (VIP) for Non-Volatile Memory Express (NVMe) announcement from Synopsys is the first fruit issued from the acquisition of ExpertIO. With the proliferation of Nand Flash based storage equipment, or Solid State Drives (SSD), the move from pure SATA based solution was to be expected, sooner or later. Not because… Read More