As verification continues to be a key ingredient in successful design implementation, new approaches have been tried to balance cost, time to results and comprehensive analysis in designs that require large patterns in some application like Image Processing. Simulation environments are well proven, and designers tend to … Read More

Tag: verification

DVCon 2018 Mentor Graphics and SemiWiki

DVCon turns 30 this year which is a very big deal. My oldest child also turns 30 this year which really puts things in perspective looking back at what we have all accomplished during that time. DVCon originally started as a user’s group at the 1988 Design Automation Conference in Anaheim California and the rest as they say is history.… Read More

System Level Formal

Two recently announced vulnerabilities in major processor platforms should remind us that bugs don’t organize themselves to appear only in domains we know how to test comprehensively. Both Meltdown and Spectre (the announced problems) are potential hardware system-level issues allowed by interactions between speculative… Read More

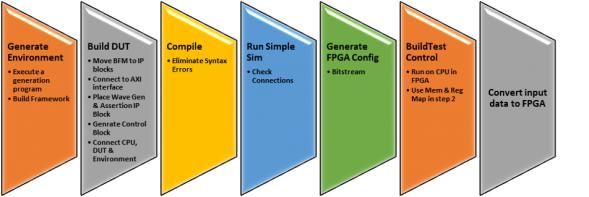

What are you ready to mobilize for FPGA debug?

There are 3 common misconceptions about debugging FPGA with the real hardware:

[LIST=1]

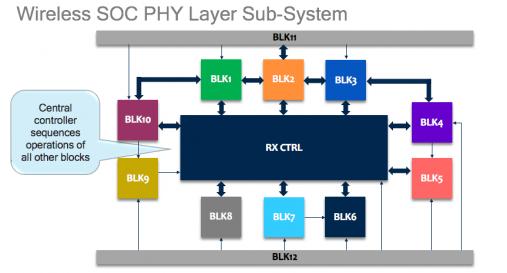

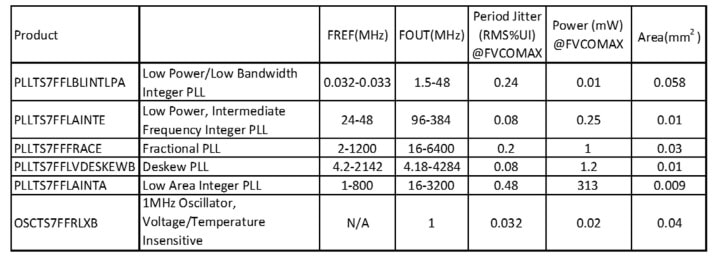

Silicon Creations talks about 7nm IP Verification for AMS Circuits

Designing at 7nm is a big deal because of the costs to make masks and then produce silicon that yields at an acceptable level, and Silicon Creations is one company that has the experience in designing AMS IP like: PLL, Serializer-Deserializer, IOs, Oscillators. Why design at 7nm? Lots of reasons – lower power, higher speeds,… Read More

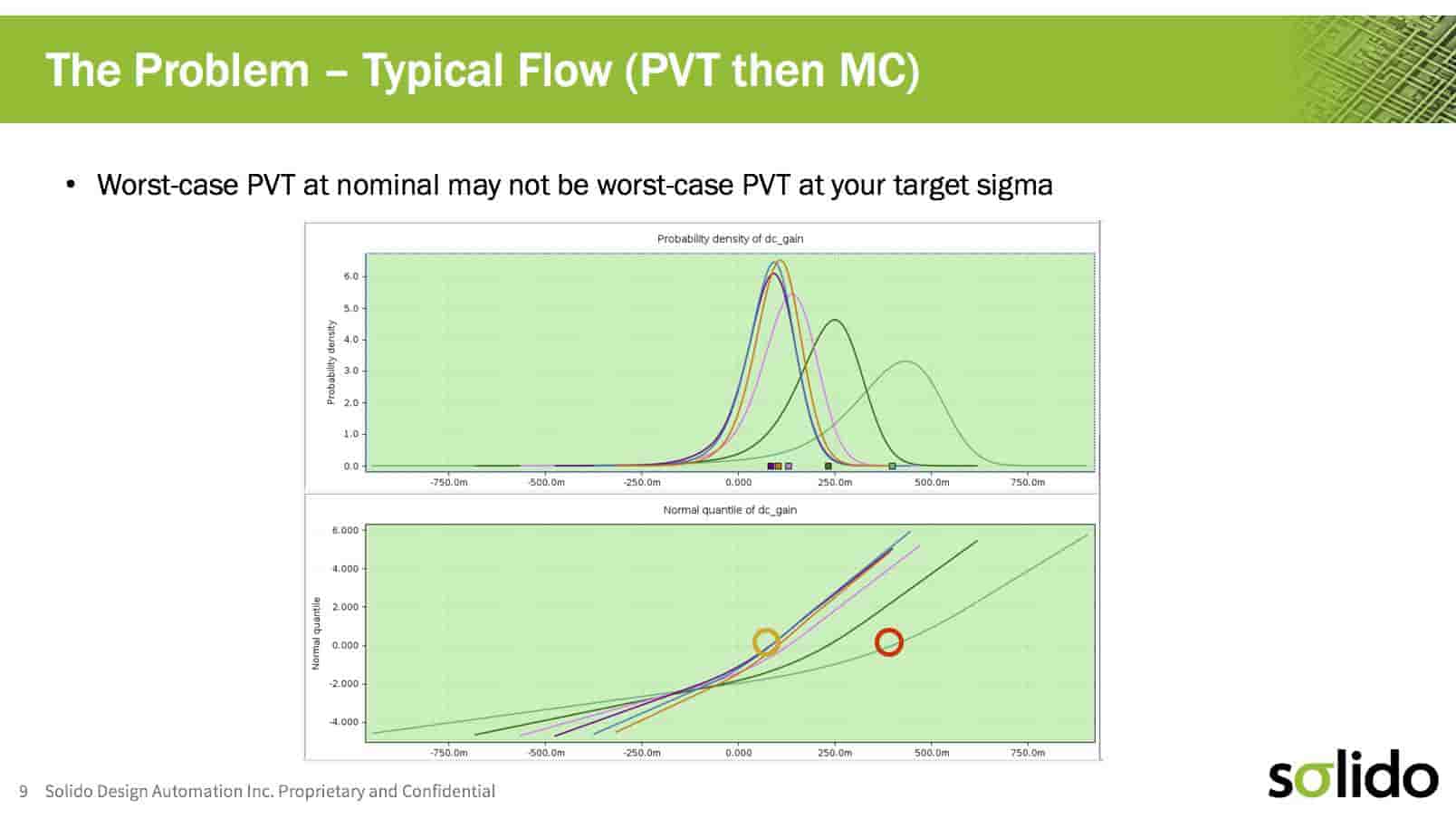

A better way to combine PVT and Monte Carlo to improve yield

TSMC held its Open Innovation Platform Forum the other week on September 13[SUP]th[/SUP]. Each year the companies that exhibit at this event choose to highlight their latest technology. One of the most interesting presentations that I received during the event was from Solido. In recent years they have produced a number of groundbreaking… Read More

Verification Trends: 2016

Periodically Mentor does us all a big favor by commissioning a survey of verification engineers across the world to illuminate trends in verification. This is valuable not only to satisfy our intellectual curiosity but also to help convince managers and finance mandarins that our enthusiasm to invest in new methods and tools … Read More

Improved Memory Design, Characterization and Verification

My IC design career started out with DRAM design, characterization and verification back in the 1970’s, so I vividly recall how much SPICE circuit simulation was involved, and how little automation we had back in the day, so we tended to cobble together our own scripts to help automate the process a bit. With each new process… Read More

Webinar: Fast-Track to Riviera-PRO

Whether you’re right out of college, starting on your first design, a burn-and-churn designer thinking there must be a better way or an ASIC designer wanting to do a little prototyping, this webinar may be for you. It’s a fast start on using the Aldec Riviera-PRO platform for verification setup, run and debug, and more. There are … Read More

Cadence Explores Smarter Verification

Verification as an effectively unbounded problem will always stir debate on ways to improve. A natural response is to put heavy emphasis on making existing methods faster and more seamless. That’s certainly part of continuous improvement but sometimes we also need to step back and ask the bigger questions – what is sufficient … Read More