Yesterday evening was EDAC’s first mixer. I assume the first of a regular event. It was held in Mountain View in the old train station which is now the Savvy Cellar wine bar. I had a nice glass of rosé from Provence that reminded me of the years that I lived in the south of France. Some of the money we spent went to charity, to the Mountain… Read More

Tag: verification

A Methodology for Assertion Reuse in SoC Designs

As your SoC design can contain hundreds of IP blocks, how do you verify that all of the IP blocks will still work together correctly once assembled? Well, you could run lots of functional verification at the full-chip level and hope for the best in terms of code coverage and expected behavior. You could buy an expensive emulator to … Read More

Verifying DRC Decks and Design Rule Specifications

DRVerify is part of the iDRM design rule compiler platform from Sage DA, something that I have been personally involved with for the past three years. DRVerify is mainly used to verify third party design rule check (DRC) decks and ensure that they correctly, completely and accurately represent the design rule specification. In… Read More

Verification of Power Delivery Networks

Power delivery networks (PDN) are the metal structures on a chip that delivers the power. In a high-end desktop SoC this might be delivering as much as 150W, and with voltages around 1V that means over 150 amps of current. Clearly getting the PDN correct is critical for a correctly functioning chip. One of the challenges to verifying… Read More

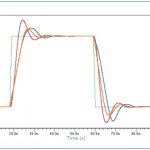

Speeding Up AMS Verification by Modeling with Real Numbers

My first introduction to modeling an AMS behavior using a language was back in the 1980’s at Silicon Compilers using the Lsim simulator. Around the same time the VHDL and Verilog languages emerged to handle the modeling of both digital and some analog behaviors. The big reason to model analog behavior with a language is for… Read More

Jasper Goes to DVCon

As usual, since they are firmly in the verification space, Jasper will have a number of things going on at DVCon 2014 which is March 3-6th at the Doubletree in San Jose. In the exhibition hall they are at booth #402.

Jasper will be happy to talk to you about anything, I’m sure, but the focus this year is on the JasperGold Security… Read More

How Do You Verify a NoC?

Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

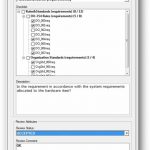

If requirements ask for it, it had better be there

Engineers are known for their attention to detail and precision in thinking, but sometimes still struggle during compliance audits. This is especially true the longer a list of requirements becomes, especially unstructured lists kept in spreadsheets and on Post-It notes.

It gets even more complicated, because in defense circles… Read More

Have you Tried ALDEC?

I must admit. I was too comfortable. Let me explain, I’m a ModelSim guy from Mentor Graphics. I did not really think nor care much of the other RTL simulator options. How could someone build a better tool with respect to simulation? Let me introduce you to Aldec. Aldec was founded in 1984 by Dr. Stanley M. Hyduke. 30 years later they are… Read More

JasperGold COV App, the Swiss Army Knife for Verification

At the Jasper Users Group meeting in October Rajeev Ranjan presented on the JasperGold COV App which he described as the Swiss army knife for verification. It comes in many sizes and contains many useful tools.

The primary goal of COV is to provide coverage metrics:

- stimuli coverage: how restrictive is the design behavior under