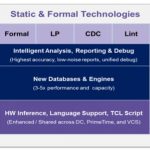

Synopsys announced verification compiler a couple of months ago and dropped hints about their static and formal verification. They haven’t announced anything much for a couple of years and it turns out that the reason was that they decided that the technology that they had, some internally developed and some acquired, … Read More

Tag: verification

Jasper at DAC

Wait, didn’t Cadence just acquire Jasper. Why is there a Jasper at DAC post?

So the big event is lunch on Tuesday, on Treasure Island. For out of towners that is the island in the middle of the bay bridge (actually just half of it). Food trucks, awesome views of the bay, and really cool street performers. There will be street magic,… Read More

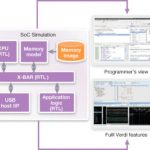

Hardware/Software Debug

One of the big challenges with modern SoCs is that they have a complex software component as well as the hardware itself being complex. Some aspects of the hardware can be debugged independently of the software and vice versa, but often it is not immediately clear whether the source of a problem is hardware, software or some interaction… Read More

Eric Esteve to Present during CDN Live 2014 in Munich

I will have the privilege to give an “IP Outlook” presentation during next Cadence event in Europe, CDN-Live to be held in Munich the 19[SUP]th[/SUP] to 21[SUP]st[/SUP] of May. I had a look at the agenda, and the conference will be pretty busy, especially on Tuesday, as there will be more than fifty presentations, starting at 10:30… Read More

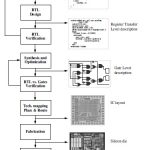

RTL Designers Can Win a GoPro Camera at DAC

DACis just 33 days away and who wouldn’t want a cool GoPro camerato play with? Your manager will certainly want you to first check out what’s new at DAC if your job involves getting to RTL signoff on time and within budget. The creative folks at Atrenta have figured out how to attract us with the offer of winning a GoPro camera,… Read More

IP the eSilicon Way

Pop quiz: eSilicon has a big IP development group in what Asian country? If you didn’t know and you guessed, you probably got it wrong with China or India. It is Vietnam. In fact they have two sites. One in Ho Chi Minh City (that used to be called Saigon) and one in Da Nang.

At Electronic Design Process Symposium (EDPS) held last … Read More

Importance of Data Management in SoC Verification

In an era of SoCs with millions of gates, hundreds of IPs and multiple ways to verify designs through several stages of transformations at different levels of hierarchies, it is increasingly difficult to handle such large data in a consistent and efficient way. The hardware and software, and their interactions, have to be consistent… Read More

Cadence Acquires Jasper

Cadence announced today that it is acquiring Jasper Design Automation for $170M in an all-cash offer. Jasper has $24M in cash so it is really an acquisition for around $145M. i think that is around 4X revenue but I only know rumors about Jasper’s revenue numbers.

All the big 3 already have their own formal technology but the … Read More

Can the NSA Get Into Your Chip?

At DVCon Lawrence Loh and Viktor Markus Purri gave a tutorial on Formally Verifying Security Aspects of SoC Designs. Lawrence is the direector of WW application engineering and Markus is an FAE who specializes in security verification.

I’m not going to attempt to summarize an entire half-day tutorial in under 1000 words,… Read More

Power and Thermal Simulation in ESL Verification Flows

At the recent DVcon there was a keen focus on design verification and validation. Much of the attention is on Logic/circuit design verification, UVM, and IP verification. At the system level functional verification has improved to comprehend complex hardware and software interaction using Virtual Platforms/SystemC and Transaction… Read More