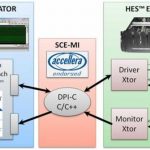

As design complexity and size is increasing, SoC verification has become one of the most difficult and time consuming tasks in the design closure.UVM (Universal Verification Methodology, an accellera initiative) is one of the best verification methodologies that support common language, coherent strategy, clarity and transparency… Read More

Tag: verification

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

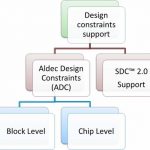

Aldec increasing the return on simulation

Debate rages about which approach is better for SoC design: simulation, or emulation. Simulation proponents point to software saving the need for expensive hardware platforms. Emulation supporters stake their claims on accuracy and the incorporation of real-time I/O. A few years back, some creative types coined the term SEmulation,… Read More

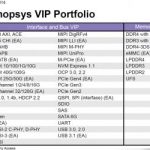

Last VIP News of 2014

It’s likely that most of the current Semiwiki readers didn’t read this article posted in 2011, comparing Cadence and Synopsys with the Soviet Union and the USA, sharing the world in 1944 during the Yalta Conference. I was explaining in my post that Synopsys’s strong influence was on Design IP when Cadence’s preferred domain was … Read More

Ensuring Safety Distinctive Design & Verification

In today’s world where every device functions intelligently, it automatically becomes active on any kind of stimulus. The problem with such intelligence is that it can function unfavorably on any kind of bad stimulus. As the devices are complex enough in the form of SoCs (which at advanced process nodes are more susceptible to … Read More

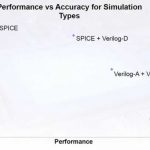

Verilog-AMS connects T-SPICE and Riviera-PRO

With advances in available IP, mixed signal design has become much easier. Mixed signal verification on the other hand is becoming more complicated. More complexity means more simulation, and in the analog domain, SPICE-based techniques grinding away on transistor models take a lot of precious time. Event-driven methods like… Read More

An Approach to Top-Down SoC Verification

We’ve blogged dozens of times about UVM– Universal Verification Methodology at SemiWiki, and all of the major EDA vendors support UVM, so you may be lulled into thinking that UVM is totally adequate for top-down SoC verification. Yesterday I had a phone discussion with Frank Schirrmeister of Cadence about a new approach… Read More

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

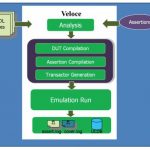

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More

Mentor Wins v Synopsys

Just a couple of days ago I read a curious press release.Mentor Graphics Corp. (NASDAQ: MENT), today announced that a Portland, Oregon jury delivered a verdict in favor of Mentor in a trial in which Mentor asserted infringement of one of its patents against Emulation and Verification Engineering S.A. (EVE) and Synopsys, Inc. (Nasdaq:… Read More