Our EDA industry loves three letter acronyms so credit the same industry for creating a five letter acronym CoWoS. Two weeks ago TSMC announced tape-out of their first CoWoS test chip integrating with JEDEC Wide I/O mobile DRAM interface, making me interested enough to read more about it. At the recent TSMC Open Innovation Platform… Read More

Tag: tsmc

SpyGlass IP Kit 2.0

On Halloween, Atrenta and TSMC announced the availability of SpyGlass IP Kit 2.0. IP Kit is a fundamental element of TSMC’s soft IP9000 Quality Assessment program that assesses the robustness and completeness of soft (synthesizable) IP.

IP Kit 2.0 will be fully supported on TSMC-Online and available to all TSMC’s soft IP alliance… Read More

Hybrids on BeO then, 3D-IC in silicon now

Once upon a time (since every good story begins that way), I worked on 10kg, 70 mm diameter things that leapt out of tubes and chased after airplanes and helicopters. The electronics for these things were fairly marvelous, in the days when surface mount technology was in its infancy and having reliability problems in some situations.… Read More

TSMC OIP Forum 2012 Trip Report!

The second annual TSMC Open Integration Platform Ecosystem Forum was last week and let me tell you it was excellent. Great update on the TSMC process technology road maps, great for networking within the fabless semiconductor ecosystem, great for seeing what’s new in EDA and IP, and great for SemiWiki. It was time well spent for … Read More

TSMC dilemma: Cadence, Mentor or Synopsys?

Looking at the Press Release (PR) flow, it was interesting to see how TSMC has solved a communication dilemma. At first, let’s precise that #1 Silicon foundry has to work with each of the big three EDA companies. As a foundry, you don’t want to lose any customer, and then you support every major design flow. Choosing another strategy… Read More

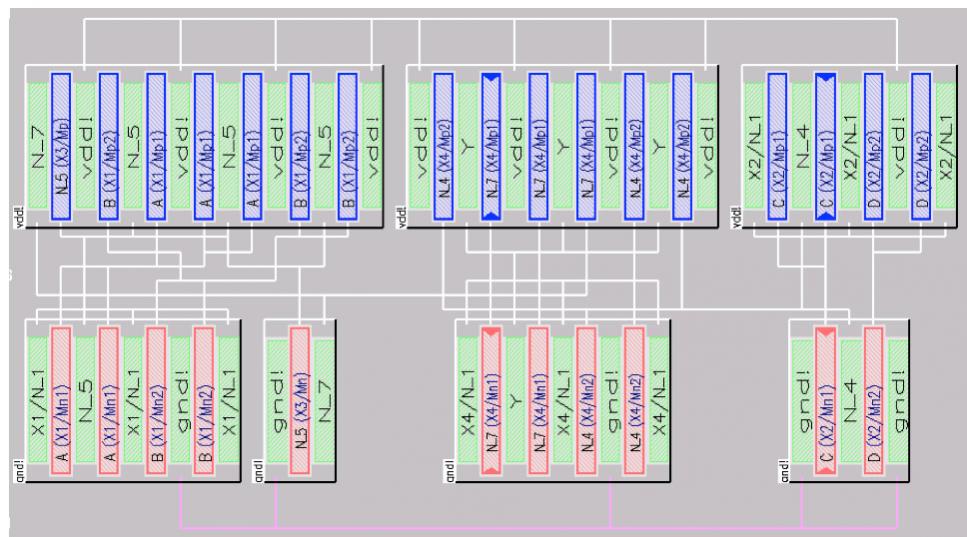

Laker3 in TSMC 20nm Reference Flow

SpringSoft, soon to be part of Synopsys but officially still a separate company for now, just announced that Laker[SUP]3[/SUP], the third generation of their layout product family, is featured in TSMC’s 20nm Custom Reference Flow.

Laker 20nm advancements include new double patterning-aware design and voltage-dependent… Read More

Soft IP Quality Standards

As SoC design has transformed from being about writing RTL and more towards IP assembly, the issue of IP quality has become increasingly important. In 2011 TSMC and Atrenta launched the soft IP qualification program. Since then, 13 partners have joined the program.

IP quality is multi-faceted but at the most basic level, an IP block… Read More

Will Paul Otellini Convince Tim Cook to Fill Intel’s Fabs?

An empty Fab is a terrible thing to waste, especially when it is leading edge. By the end of the year Intel will, by my back of the envelope calculation, be sitting with the equivalent of one idle 22nm Fab (cost $5B). What would you do if you were Paul Otellini?

Across the valley, in Cupertino, you have Tim Cook, whose modus operandi is … Read More

Mentor Graphics Update at TSMC 2012 OIP

What

In just 20 days you can get an update on four Mentor Graphics tools as used in the TSMC Open Innovation Platform (OIP). Many EDA and IP companies will be presenting along with Mentor, so it should be informative for fabless design companies in Silicon Valley doing business with TSMC.

… Read More

Taiwan Travel Explained!

Whenever people hear that I travel internationally one week a month they cringe at the thought of crowded airports, 12 hour flights, jet lag, and days packed with meetings. I generally shrug, accept the label of travel warrior, and say it is all part of doing business in the semiconductor ecosystem. But in reality, it is not as bad … Read More