If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

Tag: thermal

Don’t Miss Mentor Graphics U2U San Jose, April 21, 2015

Mentor Graphics’ User2User conference will be held next week on April 21[SUP]st[/SUP] at the San Jose DoubleTree Hotel. This one-day, free conference is the perfect opportunity to learn, network, and share with other Mentor Graphics users.

The day starts off with back-to-back keynotes that examine different aspects of the … Read More

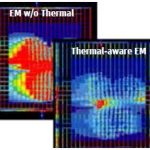

FinFET Designs Need Early Reliability Analysis

In a world with mobile and IoT devices driven by ultra-low power, high performance and small footprint transistors, FinFET based designs are ideal. FinFETs provide high current drive, low leakage and high device density. However, a FinFET transistor is more exposed to thermal issues, electro migration (EM), and electrostatic… Read More

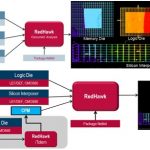

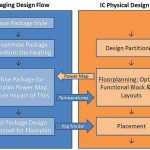

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

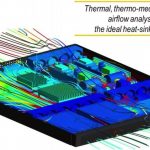

Electronic Thermal Management through Icepak

Last week my daughter was playing some games on my Google Nexus smartphone for a while when one of my friends called. When I picked up the phone, I couldn’t imagine it was so hot. There is no doubt; every electronic device today emits an order of magnitude higher heat than what it used to at most a decade ago. There is so much emphasis on … Read More

Temperature – The Fourth Aspect to Look at in SoC Design

In my career in semiconductor industry, I can recall, in the beginning there was emphasis on design completion with automation as fast as possible. The primary considerations were area and speed of completion of a semiconductor design. Today, with unprecedented increase in multiple functions on the same chip and density of the… Read More

Two New ESL Tools for Power and Thermal at DAC

Gary Smith published a list of what to see at DAC, and I noticed that he listed DOCEA Power in a category of ESL Thermal. I’ll be meeting the DOCEA engineers on Wednesday at DAC to learn more about their two newest ESL products:

- Thermal Profiler

- Power Intelligence

In general DOCEA Power tools allow you to manage power and thermal… Read More

Power and Thermal Simulation in ESL Verification Flows

At the recent DVcon there was a keen focus on design verification and validation. Much of the attention is on Logic/circuit design verification, UVM, and IP verification. At the system level functional verification has improved to comprehend complex hardware and software interaction using Virtual Platforms/SystemC and Transaction… Read More