Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

Tag: systemc

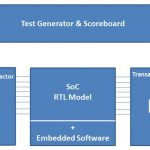

With SCE-MI, timing really is everything

In one of my favorite movies, Brad Pitt utters the only question that matters in baseball or technology management in the face of uncertainty: “Okay, good. What’s the problem?” Not surprisingly in that scene, as the question circles the table of experts used to doing things the old way, not a single one can answer it correctly in the… Read More

Develop A Complete System Prototype Using Vista VP

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More

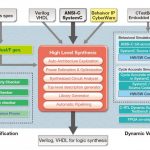

Verifying Hardware at the C-level

As more people adopt high-level synthesis (HLS) they start to worry about what is the best design flow to be using. This is especially so for verification since it forms such a large part of the effort on a modern SoC. The more people rely on HLS for producing their RTL from C, the more they realize they had better do a good job of verifying… Read More

Something old, something new in SystemC HLS

Perhaps no area in EDA has been as enigmatic as high-level synthesis (HLS). At nearly every industry event, some new-fangled tool always seems to be tabbed as the next big thing by some analyst or pundit. In a twist, the latest news is on one of the oldest tools – CybeWorkBench.… Read More

When Is a Good Time to Start Using High-Level Synthesis?

Of course if you are in the business of selling high-level synthesis (HLS) tools then the obvious answer is immediately. Start at 9am tomorrow morning. But a more realistic answer is when you are having to do something completely new. If you are working on a legacy design, perhaps with pre-existing IP, then moving the design up to … Read More

Constrain all you want, we’ll solve more

EDA tool development is always pushing the boundaries, driven in part by bigger, faster chips and more complex IP. For several years now, the trend has been developing tools that spot problems faster without waiting for the “big bang” synthesis result that takes hours and hours. Vendors, with help from customers, are tuning tools… Read More

Configurable System IP from a Tool Provider

While I have previously blogged on Forte’s Cynthesizer Workbench’s Interface Generator, I want to take another look from a different perspective. Watching the tool and IP together in action through public videos provided by Forte it struck me as odd what I did not consider earlier, on what should have been obvious to me – Forte is… Read More

Analysis of HLS Results Made Easier

In a recent article I discussed how easy it was to debug SystemC source code as shown in a video published on YouTube by Forte Design Systems. I also commented on the usefulness of the well-produced Forte video series. Today, I am reviewing another video in that series on analyzing high-level synthesis (HLS) results.

Cynthesizer… Read More

Easy SystemC Debugging

Electronic system design has been slowly migrating to higher level languages such as SystemC for more than a decade now. SystemC is an open source C++ library that has emerged as a standard for high-level design and system modeling. Writing code in SystemC has several advantages which I won’t elaborate on in this article, though… Read More