Like many people, I have been adding automation to my home, and the number of connected devices I use has slowly but steadily increased. These include light bulbs, cameras, switches, a thermostat, a voice assistant, etc. Between them, they know when I am home or away, and have the ability to record images and sound. In addition to … Read More

Tag: synopsys

#56thDAC SerDes, Analog and RISC-V sessions

The good news is that the next five DAC events will take place in Moscone Center in San Francisco! If going to Las Vegas from the Bay area is an easy trip, coming from Europe to Las Vegas makes it a 24+hours journey… One obvious consequence was the poor attendance to the exhibition floor. But let’s be positive and notice that the number… Read More

Semiconductor IP Security Issues

Every morning I read the headlines from SemiWiki, CNN, LinkedIn and my Twitter feed, and it seems like every week that I read about another security breach that makes me wonder if anything online is secure. Companies try to harden their web sites, IT infrastructure and even their electronic products from being exploited or tampered… Read More

The IoT will meet 5G soon, but not with the old SIM cards

By now you have probably realized that 5G is a lot more than an incremental change from previous 3G and 4G cellular technology. For instance, 5G will be used to connect our phones in completely new ways, such as with microcells in urban areas using mm-wavelength signals. 5G will also include two low power protocols that are intended… Read More

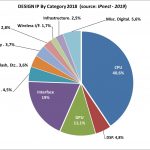

Design IP in 2018: Synopsys and Cadence Increase Market Share…

…but ARM, Imagination, MIPS or Ceva have declined and lose market share. Semiconductor design IP market is still doing good in 2018, with 6% growth year over year. It’s half the growth rate seen in 2017, 2016 and 2015 and the growth decline is imputable to bad results from ARM, the market leader, but also from Imagination (#4), MIPS… Read More

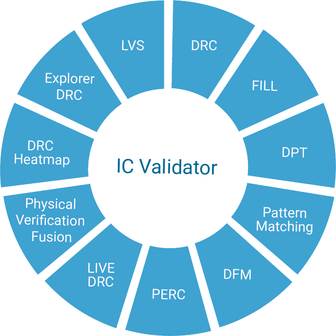

Complex Validation Requires Scalable Measures

The famous Olympic motto Citius, Altius, Fortius, which is the Latin words for “Faster, Higher, Stronger” to a considerable degree can be adapted to our electronics industry. Traditionally the fundamental metrics we used for measuring the quality of results (QoRs) are performance, power, and area (PPA). Amidst… Read More

EDA Update 2019

Over the last six years EDA has experienced yet another disruption not unlike the Synopsys acquisition of Avant! in 2001 which positioned Synopsys for the EDA lead they still enjoy today. Or the hiring of famed venture capitalist Lip-Bu Tan in 2009 to be the CEO of struggling EDA pioneer Cadence Design Systems. Under Lip-Bu’s… Read More

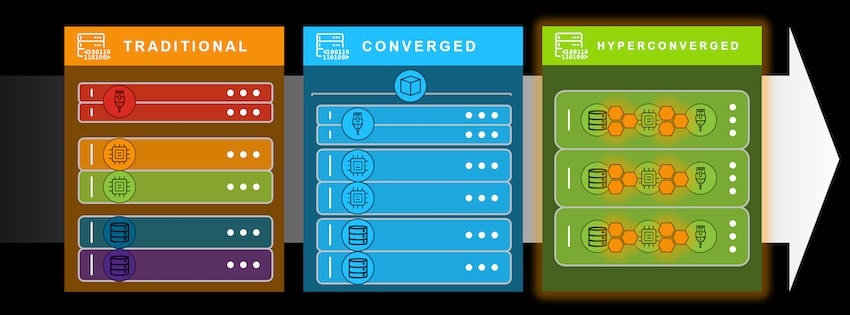

IC Implementation Improved by Hyperconvergence of Tools

Physical IC design is a time consuming and error prone process that begs for automation in the form of clever EDA tools that understand the inter-relationships between logic synthesis, IC layout, test and sign-off analysis. There’s even an annual conference called ISPD – International Symposium on Physical Design… Read More

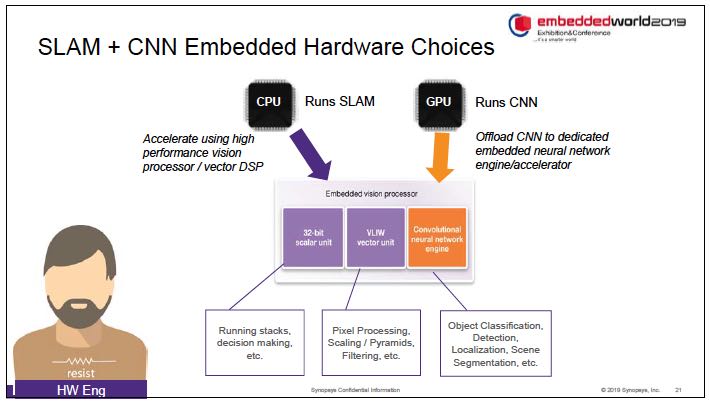

Using ML to Build Efficient Low Power Platforms for Augmented Vision

We are all pretty familiar with augmented reality, where real world images are overlaid with computer generated images, graphics and even audio. Of course, our first exposure to augmented reality might have been images of heads up displays in fighter jets or perhaps in the movie The Terminator. Augmented reality is moving rapidly… Read More

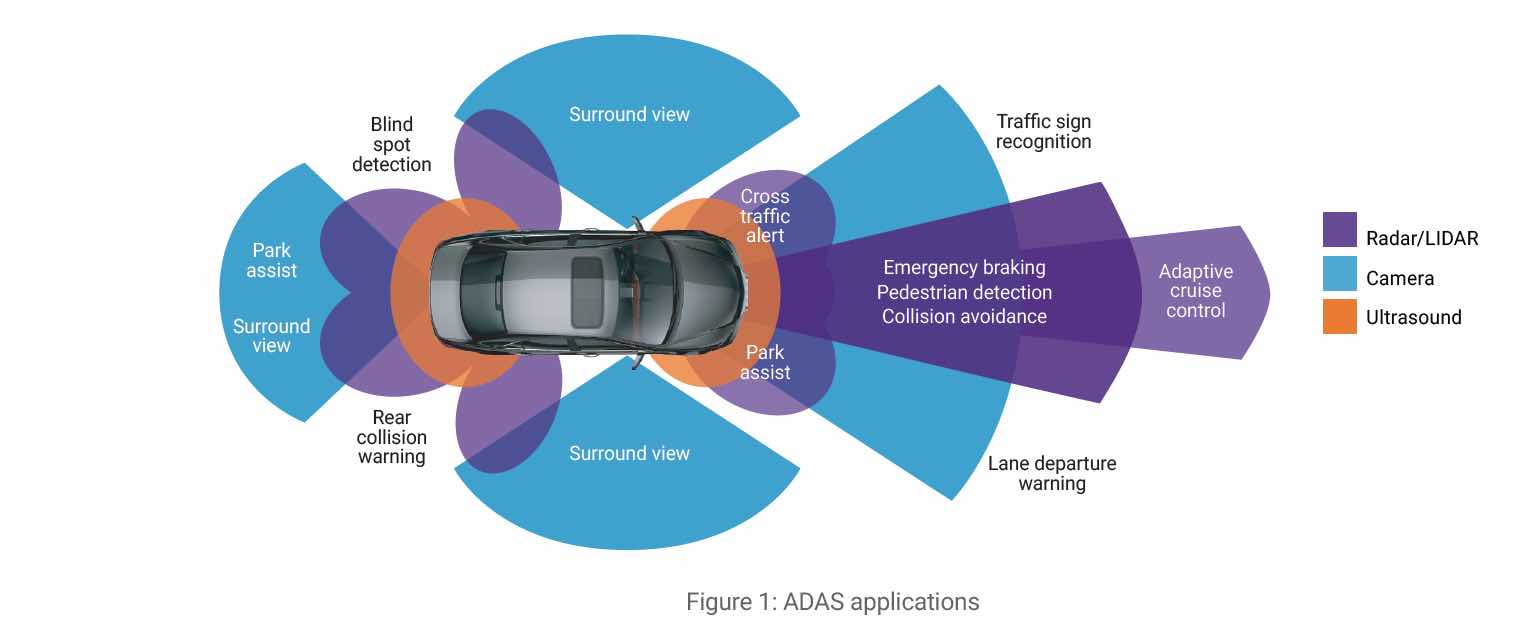

Accelerating SOC Development for Automobile Applications

No area of electronics is moving faster than automotive semiconductors. Everyone has been talking about the increasing electronics content of automobiles for decades. With Advanced Driver Assistance System (ADAS) and autonomous driving becoming a reality the pace has picked up even more. These new designs combine just about… Read More