Over the last few years, transformers have been fundamentally changing the nature of deep learning models, revolutionizing the field of artificial intelligence. Transformers introduce an attention mechanism that allows models to weigh the importance of different elements in an input sequence. Unlike traditional deep learning… Read More

Tag: synopsys

The True Power of the TSMC Ecosystem!

The 15th TSMC Open Innovation Platform® (OIP) was held last week. In preparation we did a podcast with one of the original members of the TSMC OIP team Dan Kochpatcharin. Dan and I talked about the early days before OIP when we did reference flows together. Around 20 years ago I did a career pivot and focused on Strategic Foundry Relationships.… Read More

Podcast EP185: DRAM Scaling, From Atoms to Circuits with Synopsys’ Dr. Victor Moroz

Dan is joined by Dr. Victor Moroz, a Synopsys Fellow engaged in a variety of projects on leading edge modeling Design-Technology Co-Optimization. He has published more than 100 technical papers and over 300 US and international patents. Victor has been involved in many technical committees and is currently serving as an Editor… Read More

WEBINAR: Why Rigorous Testing is So Important for PCI Express 6.0

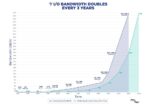

In the age of rapid technological innovation, hyperscale datacenters are evolving at a breakneck pace. With the continued advancements in CPUs, GPUs, accelerators, and switches, faster data transfers are now paramount. At the forefront of this advancement is PCI Express (PCIe®), which has become the de-facto standard of interconnect… Read More

Synopsys Expands Synopsys.ai EDA Suite with Full-Stack Big Data Analytics Solution

More than two years ago, Synopsys launched its AI-driven design space optimization (DSO.ai) capability. It is part of the company’s Synopsys.ai EDA suite, an outcome of its overarching AI initiative. Since then, DSO.ai has boosted designer productivity and has been leveraged for 270 production tape-outs. DSO.ai uses machine… Read More

Interface IP in 2022: 22% YoY growth still data-centric driven

We have shown in the “Design IP Report” 2022 that the market share of the wired Interface IP category is a growing part of the total IP, and that this trend is confirmed year after year. The interface IP category has moved from 18% share in 2017 to 25% in 2022.

During the 2010-decade, smartphone was the strong driver for the IP industry,… Read More

ISO 21434 for Cybersecurity-Aware SoC Development

The automotive industry is undergoing a remarkable transformation, with vehicles becoming more connected, automated, and reliant on software. While these advancements promise convenience, comfort and efficiency to the consumers, the nature and complexity of the technologies also raise concerns for functional safety … Read More

Key MAC Considerations for the Road to 1.6T Ethernet Success

Ethernet’s continual adaptation to meet the demands of a data-rich, interconnected world can be credited to the two axes along which its evolution has been propelled. The first axis emphasizes Ethernet’s role in enabling precise and reliable control over interconnected systems. As industries embrace automation… Read More

Podcast EP178: An Overview of Advanced Power Optimization at Synopsys with William Ruby

Dan is joined by William Ruby, director of product management for Synopsys Power Analysis products. He has extensive experience in the area of low-power IC design and design methodology, and has held senior engineering and product marketing positions with Cadence, ANSYS, Intel, and Siemens. He also has a patent in high-speed… Read More

Next-Gen AI Engine for Intelligent Vision Applications

Artificial Intelligence (AI) has witnessed explosive growth in applications across various industries, ranging from autonomous vehicles and natural language processing to computer vision and robotics. The AI embedded semiconductor market is projected to reach $800 billion by year 2030. Compare this with just $48 billion… Read More