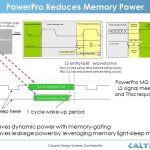

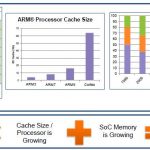

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More

Tag: soc

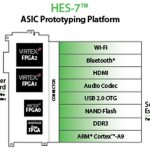

Zynq out of the box, in FPGA-based prototyping

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More

How much SRAM proportion could be integrated in SoC at 20 nm and below?

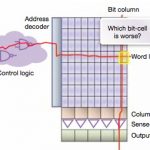

Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More

Static Timing Analysis for Memory Characterization

Modern SoC (System On Chip) designs contain a larger number of RAM (Random Access Memory) instances, so how do you know what the speed, timing and power are for any instance? There are a couple of approaches:

[LIST=1]

Improving FPGA Prototype Debugging

FPGA Prototyping is growing in popularity as a method to get an SoC design into hardware running at clock speeds up to 100MHz or so. One downside during traditional FPGA prototyping debug is the limited number of internal signals that you can observe while trying to chase down bugs in the hardware design in the presence of running … Read More

SoC emulation syncs up with SuperSpeed USB

They say what adds value is to take something difficult and make it look simple. USB looks so simple when it is done right, but designers know it can be one of the more tempermental features in an SoC, especially in the latest SuperSpeed incarnation.… Read More

Altera’s Real Impact with ARM based SOC FPGAs

At the annual Linley Processor Conference this past week a number of chip vendors proposed a raft of new networking solutions directed at solving today’s bandwidth issues. Perhaps the overall highlight of the conference was the recognition by Keynote Speaker Linley Gwennap of the shift that is taking place towards ARM based solutions.… Read More

The Middle is A Bad Place to Be if You’re a CPU Board

In a discussion with one of my PR network recently, I found myself thinking out loud that if the merchant SoC market is getting squeezed hard, that validates something I’ve been thinking – the merchant CPU board market is dying from the middle out.… Read More

Current Embedded Memory Solutions Are Inadequate for 100G Ethernet

With an estimated 7 billion connected devices, the demand for rich content, including video, games, and mobile apps is skyrocketing. Service providers around the globe are scrambling to transform their networks to satisfy the overwhelming demand for content bandwidth. Over the next few years, they will be looking to network… Read More

SpringSoft Laker vs Tanner EDA L-Edit

Daniel Payne recently blogged some of the integration challenges facing Synopsys with their impending acquisition of SpringSoft. On my way back from San Diego last week I stopped by Tanner EDA to discuss an alternative tool flow for users who find themselves concerned about the Laker Custom Layout road map.

Design of the analog… Read More