Shelly Henry is the CEO and Co-Founder of MooresLabAI, bringing over 25 years of semiconductor industry experience. Prior to founding MooresLabAI, Shelly led silicon teams at Microsoft and ARM, successfully delivering chips powering billions of devices worldwide. Passionate about driving efficiency and innovation, Shelly… Read More

Tag: soc integration

LIVE WEBINAR: Automating the Integration Workflow with IP Centric Design

Subsystem and full-chip integration plays a crucial role in any project – particularly for large SoCs. Our upcoming webinar on April 30 confronts the typical challenges of this process and provides a detailed view into how IP centric design can help you solve them. Join us to learn how transforming your design flow can help your… Read More

MIPI D-PHY IP brings images on-chip for AI inference

Edge AI inference is getting more and more attention as demand grows for AI processing across an increasing number of diverse applications, including those requiring low-power chips in a wide range of consumer and enterprise-class devices. Much of the focus has been on optimizing the neural network processing engine for these… Read More

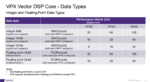

DSP IP for High Performance Sensor Fusion on an Embedded Budget

Whether we realize it or not, everyday applications we use depend on data gathered by sensors. We can bet that pretty much every application uses at least a couple of different types of sensors, if not more. That is because different types of sensors are better suited to collect data depending on the application, the environment … Read More

IP-XACT Resurgence, Design Enterprise Catching Up

This standard has been around in one form or another for over ten years and was then arguably ahead of its time. RTL designers were confused: ‘We already have RTL. Why do we need something else?’ I also didn’t get it. Still, the standard plugged ahead among the faithful and found traction among IP vendors. Particularly as a common format… Read More

SoC Integration – Predictable, Repeatable, Scalable

On its face System-on-chip (SoC) integration doesn’t seem so hard. You gather and configure all the intellectual properties (IPs) you’re going to need, then stitch them together. Something you could delegate to new college hires, maybe? But it isn’t that simple. What makes SoC integration challenging is that there are so many… Read More

CEO Interview: Dr. Chouki Aktouf of Defacto

“For more than 18 years, we never stopped innovating at Defacto. We are aware of EDA Mantra “Innovate or Die!”. Innovation is in our DNA, and we never stopped adding new automated capabilities to the SoC design community to help facing complexity and cost challenges, which increase every year.”

Before founding Defacto… Read More

A SoC Design Flow With IP-XACT

Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on… Read More

Webinar: Hassle-Free Bluetooth 5 SoC Design

Bluetooth has always been a popular communication protocol for short-range applications, but now anticipating BT5 it’s really moving into the big leagues as a significant option for IoT applications. The new standard combines ultra-low power with significantly higher range and higher performance. Ultra-low power is always… Read More

5 ways FPGA-based prototyping shrinks design time

Engineers are trained to think linearly, along the lines of we started here, then we did this, and that, and this other stuff, and here is where we ended up. If you’ve ever presented in an internal review meeting, sales conference, or a TED-like event, you know that is a dangerous strategy in winning friends and influencing people.… Read More