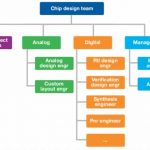

Efficient collaboration is essential to meeting tight chip design schedules. In analog and mixed signal (AMS) design, collaboration has many facets. Design tools are usually specific to roles, and handoffs are numerous, especially when moving a design to a foundry. … Read More

Tag: soc design

SoC QoS gets help from machine learning

Several companies have attacked the QoS problem in SoC design, and what is emerging from that conversation is the best approach may be several approaches combined in a hybrid QoS solution. At the recent Linley Group Mobile Conference, NetSpeed Systems outlined just such a solution with an unexpected plot twist in synthesis.

The… Read More

10 Challenges in IP Design Collaboration

Enterprise design management can be summed up in one word: collaboration. Intellectual property (IP) reuse and the success of distributed system-on-chip (SoC) design efforts depend strongly on how well designers can collaborate. As time-to-market windows have shortened, the challenges around design collaboration have… Read More

Because that is where the SoC power is

Still thinking of Sonics as just a network-on-chip company? They are pivoting to become an SoC realization company, and in their seminar at #53DAC in Austin we saw an entirely new plan focused on heisting an extremely valuable commodity everyone else is missing.… Read More

"Re-Inventing" Tapeout Sign-off — Applying Big Data Techniques to Electrical Analysis

A common SoC design methodology in current use starts with preparation of the physical floorplan — e.g., block/pin placement, global clock domain and bus signal planning, developing the global/local power distribution (and dynamic power domain management techniques). Decoupling capacitor estimated densities and… Read More

S2C tutorial and PROTOTYPICAL debut at DAC

It’s been a busy few days here in Canyon Lake, and we’re ready to share exciting news in advance of #53DAC coming up on Monday, June 6[SUP]th[/SUP]. S2C is offering a technical program tutorial on “Overcoming the Challenges of FPGA Prototyping” followed by the launch of our latest book project, “PROTOTYPICAL”, including a field… Read More

Sonics opens new strategy for SoC energy processing

Back in February when we shared the Sonics philosophy on the ICE-Grain Power Architecture for hardware-based SoC power management, I speculated we’d know more by DAC 2016. Sonics is hitting the road with a new live seminar coming to Silicon Valley this month and Austin during DAC – and the news is big.… Read More

Enterprise Design Management Engineered for SoCs

In my initial look at ClioSoft’s design management system created from the ground up for the semiconductor industry, I made the opening case for managing and reusing IP across an ASIC design organization. Let’s for a moment say we agree on the need for an enterprise software package to do design management… Read More

Debugging is the whole point of prototyping

The prototype is obviously the end goal of FPGA-based prototyping, however success of the journey relies on how quickly defects can be found and rectified. Winning in the debug phase involves a combination of methodology, capability, and planning. Synopsys recently aired a webinar on their HAPS environment and its debug ecosystem.… Read More