Well it comes as no surprise to those that use and design them, that PLL’s are a world unto themselves and very complicated indeed. With PLL’s we are talking about analog designs that rely on ring oscillators or LC tanks. They are needed on legacy nodes, like the ones that IoT chips are based on, and they are crucial for high speed advanced… Read More

Tag: serdes

CEO Interview: Alan Rogers of Analog Bits

It has been incredible to watch the Semiconductor IP market grow from millions to billions of dollars during my career in Silicon Valley. In fact, more than half of my professional experience involves IP so when I talk about what it takes to be successful it is certainly worth a listen.

In my opinion the key ingredient to a successful… Read More

CTO Interview: Jeff Galloway of Silicon Creations

It is clear that IP companies play an important role in modern semiconductor design, in fact, I would say that they are imperative. Founded in 2006, Silicon Creations is one of those imperative IP companies that provide silicon proven IP to customers big and small around the world. To follow-up on our conversation with Silicon Creations… Read More

DesignCon 2017 and Mentor Graphics

It’s hard to believe but this is DesignCon #22 and being a Silicon Valley conference I have attended my fair share of them. This year it seems like high speed communications will take the lead followed by the latest on PCB design tools, power and signal integrity, jitter and crosstalk, test and measurement tools, parallel … Read More

Analog Bits and TSMC!

As a long time semiconductor IP professional I can tell you for a fact that it is one of the most challenging segments of semiconductor design. Given the growing criticality of semiconductor IP, the challenges of being a leading edge IP provider are increasing and may be at a breaking point. The question now is: What does it take to … Read More

CEO Interview: Randy Caplan of Silicon Creations

For the next installment in our series of semiconductor CEO interviews we meet with Randy Caplan from Silicon Creations. Randy has helped build the company from a small startup to one of the world’s leading providers of interface and clocking IP. Almost every new chip developed these days has a requirement for PLLs and SerDes. Since… Read More

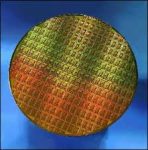

Always-On IoT – FDSOI’s Always Better? What About Wafers? (Questions from Shanghai)

Mahesh Tirupattur, EVP at low-power SERDES pioneer Analog Bits lead off the panel discussion at the recent FD-SOI Forum in Shanghai with the assertion that for anything “always on” in IoT, FD-SOI’s always better. They had a great experience porting their SERDES IP to 28nm FD-SOI (which they detailed last spring – see the ppt here… Read More

The IP Paradox: Sales are growing despite Semi Consolidation

IPnest is launching the “Interface IP Survey” since 2009, and we did it last September again. To build the survey as accurately as possible, I have followed the “divide and conquer” strategy. Interface protocols are varied, ranging from PCI Express, USB, or Ethernet, to memory controller (DDR3, DDR4, LPDDR3, LPDDR4 and more) … Read More

Interface IP year 2015: Winners and Losers

The global Interface IP market is still growing in 2015, no doubt about it. It’s interesting to zoom in the various protocols to check their respective behavior. Which protocol generates an IP business growing more than the average market? Which protocol generates a disappointing IP business? In other words, which are the winners… Read More

How Well is HSPICE Tracking Current Design Trends?

For about 5 years now Synopsys has held an HSPICE SIG event in conjunction with DesignCon. It features a small vendor faire with companies that partner with Synopsys on HSPICE flows. They also have a dinner with industry/customer speakers and provide an update on HSPICE development. Lastly there is a Q&A where customers get… Read More