Back in the Napoleonic era it was possible to manage a battle with very ad hoc methods. Sit on a horse on top of the highest hill and watch the battle unfold, send messengers out with instructions. By the First World War, never mind the second, that approach was hopelessly outdated and a much more structured way of managing a battle was… Read More

Tag: semiconductor

What Changed On My Transistor-Level Schematic?

Digital designers have used diff tools for years on their text-based HDL source code, but what about for the transistor-level IC designer, where is their diff tool for schematics or layout?… Read More

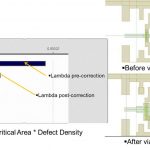

DFM Provides Proven Value

Although design for manufacturing (DFM) tools and techniques have been around for several nodes, a lot of designers remain skeptical about their actual value, especially since many products still make it successfully to market without the use of DFM.… Read More

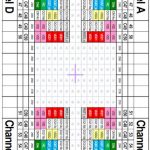

DFM Industry Survey

As part of the DFM Conference at the SPIE Advance Lithography symposium, the DFM committee is conducting an informal survey on the current state of Design For Manufacturability in the Semiconductor Industry.

Please take this anonymous 16 question survey to identify critical Design for Manufacturability (DFM) issues facing… Read More

DFM at SPIE Advance Litho show

This year’s SPIE Advanced Lithography is loaded with interesting keynotes and sessions. To help me narrow down what to see, I spoke with John Sturtevant. John is co-chair of the Design for Manufacturability through Design-Process Integration conference, and the director for technical marketing for RET products at Mentor Graphics.… Read More

AMD and GlobalFoundries?

One thing I do as an internationally recognized semiconductor blogger is listen to the quarterly conference calls of companies that drive our industry. TSMC is always interesting, I really like the honesty and vision of Dr. Morris Chang. Cadence is good, I always want to hear what Lip-Bu Tan has to say. Oracle and Larry Ellison, … Read More

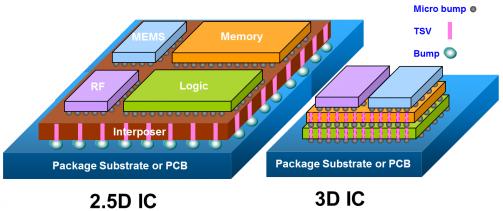

3D Standards

At DesignCon this week there was a panel on 3D standards organized by Si2. I also talked to Aveek Sarkar of Apache (a subsidiary of Ansys) who is one of the founding member companies of the Si2 Open3D Technical Advisory Board (TAB), along with Atrenta, Cadence, Fraunhofer Institute, Global Foundries, Intel, Invarian, Mentor, Qualcomm,… Read More

Semiconductor Packaging (3D IC) Emerging As Innovation Enabler!

The ASIC business is getting more and more complicated. The ability to produce innovative die at a competitive price to solve increasingly complex problems just isn’t enough. The technology required to package that die is now front and center.

Here, at the junction of advanced design, process technology and state-of-the art … Read More

The Semiconductor Landscape In A Few Years?

Looking at the huge gap between the revenue of semiconductor design and manufacturing (~$300B) and that of EDA tools, services and silicon IP combined (~6B) inspired me to look more deeply into the overall arena of semiconductors in today’s context and possibly decipher some trends which should emerge in near future. Although… Read More

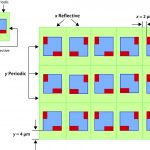

Advanced Memory Cell Characterization with Calibre xACT 3D

Advanced process technologies for manufacturing computer chips enable more functionality, higher performance, and low power through smaller sizes. Memory bits on a chip are predicted to double every two years to keep up with the demand for increased performance.

To meet these new requirements for performance and power, memory… Read More