LTE (Long Term Evolution) is the true 4G standard for cellular and, over time, wireless internet. In fact it is several different standards with different levels of performance. LTE will eventually be the only technology used in cellular, voice will simply be Voice-over-IP (VoIP, the same technology that companies like Skype… Read More

Tag: semiconductor

Sequential Power Optimization

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock… Read More

Anyone Can Build a Phone

Today’s Dilbert cartoon is about how anybody can build a smart phone. As if it was a technical problem these days. But back in the mid-90s it really was. All the contract manufacturers like Solectron and others figured that since they could build a PC they could build a phone. It turned out that building radios was really hard.… Read More

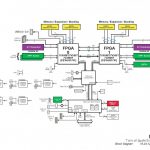

ASIC Prototyping: Dini Group and Tektronix

Collaboration in EDA is nothing new, however you may not be aware of how the Dini Group and Tektronix have worked together on an FPGA prototyping platform to address issues like debugging with full visibility across an entire multi-FPGA design. At SemiWiki we’ve blogged a couple of times so far about the new debug approach… Read More

Internet of Things, My Bluetooth Headset

A catchy phrase used by bloggers and journalists these days is “Internet of Things“, or IoT if you prefer acronyms. All of this is made possible by EDA tools in the hands of SoC designers to create useful products like my Jawbone ICON bluetooth headset. Tonight I discovered that I could customize my bluetooth headset… Read More

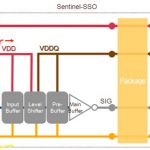

Apache on Signal Integrity

Matt Elmore has a two-part blog about the growing complexity of signal integrity analysis, both on the chip itself and the increasingly complex analysis required to make sure that signals (and power) get in and out of the chip from the board cleanly, especially to memory, which requires simultaneous analysis of chip-package-system… Read More

EDS Fair: Dateline Yohohama

Electronic Design and Solutions Fair (EDSF) was held in Yokohama Japan from Wednesday to Friday last week. It was held at the Pacifico Hotel, somewhere I have stayed several times, not far from the Yokohama branch of Hard Rock Cafe and, what used to be at least, the biggest ferris-wheel in the world.

Atrenta was one of the many companies… Read More

How much SRAM proportion could be integrated in SoC at 20 nm and below?

Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More

Is The Fabless Semiconductor Ecosystem at Risk?

Ever since the failed Intel PR stunt where Mark Bohr suggested that the fabless semiconductor ecosystem was collapsing I have been researching and writing about it. The results will be a book co-authored by Paul McLellan. You may have noticed the “Brief History of” blogs on SemiWiki which basically outline the book. If not, start… Read More

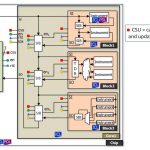

Mentor and NXP Demonstrate that IJTAG Can Reduce Test Setup Time for Complex SoCs

The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More