Timing exceptions are ways of guiding design tools, primarily synthesis and static timing analysis (STA), but these days also place & route and perhaps other tools. Most paths in a design go from one register to the next register. Both registers are on the same clock, and the design needs to ensure that the signal can make it from… Read More

Tag: semiconductor

Let’s Drive To Dearborn on 19th Sep….

[The VLC developed by Edison2, winner of the Progressive Automotive X-Prize]

Now that we have “The Very Light Car” of the world at more than 100 MPG!! Yes, this is the car developed by Edison2, one among the three winners of the Progressive Insurance Automotive X-Prize, a global competition; Edison2 won in the main stream class. … Read More

How to Benchmark a Processor

How do you benchmark a processor? It seems like it should be easy, just run some code and see how fast it is. Traditionally processors were indeed benchmarked by raw performance like GMACS, GFLOPS, memory bandwidth and so on. But in today’s world where systems have become very complex and applications very compute intensive, the… Read More

Happy Birthday Dear Cadence…

Cadence is 25 years old this year, on June 1st if you want to be precise.

The most direct ancestor of Cadence was SDA (which might or might not have stood for Solomon Design Automation). SDA was founded by Jim Solomon in 1983. It turns out that a guy I shared an office with while we were both doing our PhDs in Edinburgh Scotland was one of … Read More

Wanna Buy A Blackberry?

So Blackberry (formerly known as Research In Motion or RIM) is up for sale. Basically, apart from some cash in the bank, its main value now seems to be patents and, perhaps, some security technology. The murderers are in Cupertino and Mountain View, Apple’s iPhone (and iPad) and Google’s Android along with its licensees,… Read More

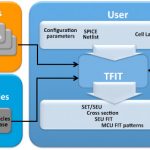

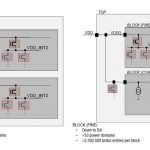

How Resistant to Neutrons Are Your Storage Elements?

There are two ways to see how resistant your designs are to single-event errors (SEE). One is to take the chip or even the entire system and put it in a neutron beam and measure how many problems occur in this extreme environment. While that may be a necessary part of qualification in some very high reliability situations, it is also … Read More

Electronic System Level: Gary Smith

Gary Smith has been talking about how the electronic system level (ESL) is where the future of EDA lies as design teams move up to higher levels encompassing IP blocks, high level synthesis, software development using virtual platforms and so on. At DAC this year in Austin he talked about how the fact that EDA controls the modeling… Read More

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

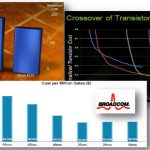

Intel Is Continuing to Scale While Others Pause

Back in May, William Holt, EVP of technology and manufacturing at Intel gave a presentation to analysts entitled Advancing Moore’s Law, Imperatives and Opportunity. A pdf of the presentation is available here. I just saw it for the first time today and I’m not sure how to get my head around it. It starts off with a lot … Read More

SEMICON Taiwan 3D

SEMICON Taiwan is September 3rd to 6th in TWTC Nangang Exhibition Hall. Just as with Semicon West in July in San Francisco, there is lots going on. But one special focus is 3D IC. There is a 3DIC and substrate pavilion on the exhibit floor and an Advanced Packaging Symposium. Design tools, manufacturing, packaging and testing solutions… Read More