This fall there seems to be a bumper harvest of cores. Today Imagination Technologies announced their latest core for image signal processing. Like all of their cores, it is designed to be part of an SoC and is designed to work with other Imagination cores to build a complete image processing system. In particular, it is designed … Read More

Tag: semiconductor

TowerJazz and Silvaco BFF

Last week was the TowerJazz Technology Fair 2013. TowerJazz is the fourth biggest foundry in the world after TSMC, GF and UMC. They have fabs in Newport Beach (the old Jazz, itself with roots in Rockwell), two in Israel (the old Tower, with roots in National Semiconductor) and one in Japan (acquired from Micron). The technology fair… Read More

The Pelican Has Landed: Formal on an Unannounced ARM Processor

At the Jasper Users’ Group, Alex Netterville of ARM presented about how ARM are using formal on an unannounced processor code-named Pelican. Don’t read the presentation trying to find out information about Pelican itself, there isn’t any. That wasn’t the topic. Alex has been using formal approaches… Read More

Running Multiple Operating Systems: Hypervisors

How do you run multiple operating systems on the same processor? You use virtualization and you run a hypervisor underneath all the so-called “guest” operating systems. So what is virtualization?

Virtualization started with VM/370 developed in 1972 at IBM (the current version is still in use). Here is how it works.… Read More

Data Management in Russia

Milandr is a company based in Moscow that makes high reliability semiconductor components for the aerospace, automotive and consumer markets, primarily in Russia. They work with multiple foundries, including X-FAB and TSMC in technologies from 1um down to 65nm. Corporate headquarter and main IC design house is located in Russian… Read More

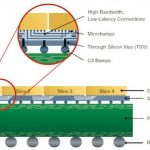

Xilinx and TSMC: Volume Production of 3D Parts

A couple of weeks ago, Xilinx and TSMC announced the production release of the Virtex-7 HT family, the industry’s first heterogeneous 3D ICs in production. With this milestone, all Xilinx 28nm 3D IC families are now in volume production. These 28nm devices were developed on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS)… Read More

Dassault Patent on Hierarchy Management

Dassault have recently been granted a patent on their approach to managing design hierarchy. I asked them how long it took from filing the patent until it was granted and they said the whole process had taken 8 years. It is a bit of an indictment of the patent system when it takes 8 years, also known as 4 or 5 process nodes, for a patent to… Read More

nVidia: Virtual Platform/Emulation Hybrid

I was the VP marketing at VaST Systems Technology and then at Virtutech. Both companies sold virtual platform technology which consisted of two parts:

- an extremely fast processor emulation technology that actually worked by doing a binary translation of the target binary code (e.g. an ARM) into the native instruction set of the

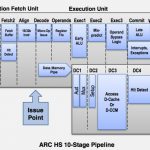

Synopsys Creates a High-performance ARC Core

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware… Read More

GlobalFoundries and ARM

GlobalFoundries had several interesting things at the ARM TechCon last week. Firstly, GlobalFoundries won the best in show award in the chip design category recognizing the best-in-class technologies introduced since the last TechCon.

Earlier in the summer GlobalFoundries and ARM announced the ARM Cortex-A12 processor,… Read More