In the modern electronic world, it’s difficult to imagine any system working as a whole without MEMS (Micro-electromechanical Systems) such as pressure sensors, accelerometers, gyroscopes, microphones etc. working in sync with other ICs. Specifically in AMS (Analog Mixed-Signal) semiconductor designs, there can be significant… Read More

Tag: semiconductor design

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

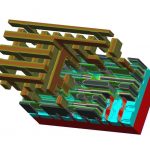

What Can Accelerate 3D Semiconductor Manufacturing?

In the beginning of this decade there was a lot of buzz around 3D chip manufacturing. Many EDA tools were developed to facilitate semiconductor designs in 3D space. Naturally, we are moving to the edge on 2D without much room to further squeeze transistors and interconnect. However, lately I haven’t heard much about 3D products.… Read More

Cadence Grows VIP Business – What’s New?

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

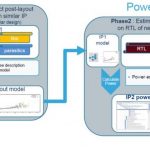

ST Endorses PowerArtist with ARM Cores & FDSOI libs

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

But I Never Have Seen a Synchronizer Failure

You may say, “Why should I worry about synchronizer failures when I have never seen one fail in a product?” Perhaps you feel that the dual-rank synchronizer used by many designers makes your design safe. Furthermore, those chips that have occasional unexpected failures never show any forensic evidence of synchronizer failures.… Read More

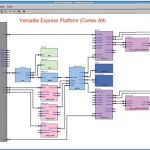

Develop A Complete System Prototype Using Vista VP

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More

Early Test –> Less Expensive, Better Health, Faster Closure

I am talking about the health of electronic and semiconductor design, which if made sound at RTL stage, can set it right for the rest of the design cycle for faster closure and also at lesser cost. Last week was the week of ITC(International Test Conference) for the Semiconductor and EDA community. I was looking forward to what ITC… Read More

Semiconductor Manufacturing in India?

Last week I heard about the Indian Cabinet approving the proposal for setting up of two Fabs in India. One led by IBM, Tower Jazzand JP Associates(an Indian business house), and the other led by HSMC(Hindustan Semiconductor Manufacturing Co.), ST Microelectronicsand Silterra. Indian Semiconductor community including IESA… Read More

Emerging Trend – Choose DRAM as per Your Design Need

Lately I was studying about new innovations in memory world such as ReRAM and Memristor. As DRAM (although it has become a commodity) has found its extensive use in mobile, PC, tablet and so on, that was an inclination too to know more about. While reviewing Cadence’s offering in memory subsystems, I came across this whitepaperwhich… Read More