As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More

Tag: rtl

Benefits of RTL Power Budgeting

Only one company at the recent DAC conference and exhibit had a set of four interacting disciplines: Fluids, Structures, Electronics and Systems. Did you guess that the company was ANSYS? I get so IC focused at times that I almost forget that chips plug into boards, that boards become systems, and that systems drive and control mechanical… Read More

Improve RTL Physically for Design Quality & Convergence

The SoC design teams are usually divided between front-end and back-end specialties. It is neither practical nor advisable to combine the two teams in order to better tackle the back-end issues upfront during the front-end design. However, a common problem is that the issues at the layout stage have very little scope for resolution… Read More

EDA Acquisition to Drive SoC realization

A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

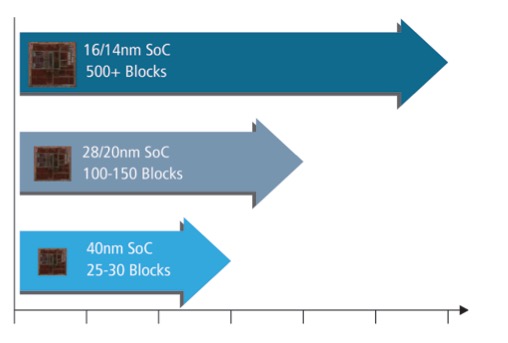

Logic Synthesis Reborn

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

A Robust Lint Methodology Ensures Faster Design Closure

With the increase in SoC designs’ sizes and complexities, the verification continuum has grown larger to an extent that the strategies for design convergence need to be applied from the very beginning of the design flow. Often designers are stuck with never ending iterations between RTL, gate and transistor levels at different… Read More

A Key Partner in the Semiconductor Ecosystem

Often we hear about isolated instances of excellence from various companies in the semiconductor industry which contribute significantly in building the overall ecosystem. While the individual excellence is essential, it’s rather more important how that excellence is utilized in a larger way by the industry to create a ‘value… Read More

Starvision Pro: Lattice Semiconductor’s Experience

During SNUG I took the opportunity to chat to Choon-Hoe Yeoh of Lattice Semiconductor about how they use Concept Engineering’s Starvision Pro product. He is the senior director of EDA tools and methodologies there.

Lattice Semiconductor is a manufacturer of low-power, small-footprint, low-cost programmable logic devices.… Read More

Verifying the RTL Coming out of a High-Level Synthesis Tool

With High-Level Synthesis (HLS) the first benefit that comes to my mind is reduced design time, because coding with C or SystemC is more efficient than low-level RTL code. What I’ve just learned is that there’s another benefit, a reduction in the amount of functional simulation required. One HLS customer was able … Read More

Expert Tool to Easily Debug RTL and Reuse in SoCs

SoC design these days has become a complex and tricky phenomenon involving integration of multiple IPs and legacy RTL code which could be in different languages, sourced from various third parties across the globe. Understanding and reusing RTL code is imperative in SoC integration which needs capable tools that can accommodate… Read More