High-level synthesis (HLS) involves the generation of an RTL hardware model from a C/C++/SystemC description. The C code is typically referred to as abehavioraloralgorithmicmodel. The C language constructs and semantics available to architects enable efficient and concise coding – the code itself is smaller, easier to write/read,… Read More

Tag: rtl

A Versatile Design Platform with Multi-Language APIs

In one of my whitepapers “SoCs in New Context – Look beyond PPA”, I had mentioned about several considerations which have become very important in addition to power, performance, and area (PPA) of an SoC. This whitepaper was also posted in parts as blogs on Semiwiki (links are mentioned below). Two important… Read More

A Brief History of Defacto Technologies

In early 2000s, semiconductor design at RTL level was gaining momentum. The idea was to process more design steps such as insertion of test and other design structures upfront at the RTL level. The design optimization and verification were to be done at the RTL level to reduce long iterations through gate level design because changes… Read More

Multi-Level Debugging Made Easy for SoC Development

An SoC can have a collection of multiple blocks and IPs from different sources integrated together along with several other analog and digital components within a native environment. The IPs can be at different levels of abstractions; their RTL descriptions can be in different languages such as Verilog, VHDL, or SystemVerilog.… Read More

Decisive Floorplanning for Faster Design Closure

Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

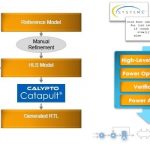

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

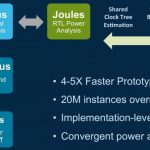

Cadence Enters the RTL Power Estimation Game

At the Cadence front-end summit last week, Jay Roy presented the Cadence Joules solution for RTL (and gate-level) power estimation. Jay is ex-Apache, so knows his way around RTL power estimation which should make Joules a product to watch. Joules connects very natively to Palladium for power characterization for realistic software… Read More

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

Power Analysis Needs Shift in Methodology

It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier … Read More

How PowerArtist Interfaces with Emulators

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More