You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

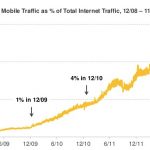

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

RTL Restructuringby Daniel Payne on 04-04-2013 at 2:34 pmCategories: EDA

Hierarchical IC design has been around since the dawn of electronics, and every SoC design today will use hierarchy for both the physical and logical descriptions. During the physical implementation of an SoC you will likely run into EDA tool limits that require a re-structure of the hierarchy. This re-partitioning will cause… Read More

We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

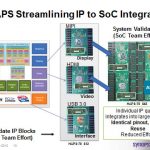

In his blog Coding Horror, Jeff Atwood wrote: “Software developers tend to be software addicts who think their job is to write code. But it’s not. Their job is to solve problems.” Whether the tool is HTML, C, or RTL, the reality is we are now borrowing or buying more software IP than ever, and integrating it into more complex designs,… Read More

Oasys Has a New CEOby Paul McLellan on 01-18-2013 at 2:21 pmCategories: EDA

Scott Seaton is the new CEO of Oasys Design Systems. Paul van Besouw, the CEO since the company’s founding, becomes the CTO. I met Scott last year when I was doing some consulting work for Carbon Design where he was VP of sales (the new VP sales at Carbon is Hal Conklin, by the way).

I talked to Scott about why he had joined Oasys. … Read More

As RTL designs in FPGA-based ASIC prototypes get bigger and bigger, the visibility into what is happening inside the IP is dropping at a frightening rate. Where designers once had several hundred observation probes per million gates, those same several hundred probes – or fewer if deeper signal captures are needed – are now spread… Read More

FPGA-based prototyping brings SoC designers the possibility of a high-fidelity model running at near real-world speeds – at least until the RTL design gets too big, when partitioning creeps into the process and starts affecting the hoped-for results.

The average ASIC or ASSP today is on the order of 8 to 10M gates, and that includes… Read More

We’re plagued by acronyms in this business. Wikipedia defines RTL as follows: “In digital circuit design, register-transfer level (RTL) is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those… Read More

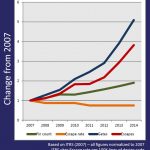

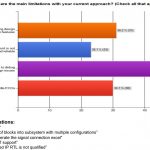

Atrenta did an online survey of their users. Of course Atrenta’s users are not necessarily completely representative of the whole marketplace so it is unclear how the results would generalize for the bigger picture, your mileage may vary. About half the people were design engineers, a quarter CAD engineers and the rest … Read More

Design for test at RTLby Paul McLellan on 07-10-2011 at 3:09 pmCategories: EDA

Design for test (DFT) imposes various restrictions on the design so that the test automation tools (automatic test pattern approaches such as scan, as well as built-in self-test approaches) will subsequently be able to generate the test program. For example, different test approaches impose constraints on clock generation… Read More