Gone are the days when analog design had its sweet space on a single chip. However, it’s the main driver in this new electronic world which is geared by Internet-of-Things, wireless, mobile, remote control and so on. How does an electronic device sense a touch by human, motion, temperature, sound etc.? It’s the analog circuitry … Read More

Tag: power

2013 Awards, and the Winner is…Power

Of all the things that designers have to worry about in the power-performance-area (PPA) equation, the most challenging is power. SoCs have reached a point that we can put a lot of stuff on them, but if we are not careful we cannot light it all up at once. Dark silicon, where we put subsystems on a chip but then don’t have enough … Read More

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

The Leading Edge Depends on What You Are Doing

At Semicon Japan a few days ago, Subi Kengeri of GlobalFoundries delivered the keynote. While he covered a number of topics, using Tokyo’s recent win of the 2020 Olympics as a hook, one major theme was the increasing importance of processes other than the bleeding edge digital processes that get all the news.

What is leading… Read More

Addressing Power at Architectural and RTL Levels

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

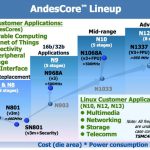

Andes: the Biggest Microprocessor IP Company You’ve Never Hear Of

I wrote in April about Andes Technology, a microprocessor IP licensing company that even the person sitting next to me, a strategic marketing guy from Qualcomm had never heard of. So, OK, if you read that earlier article you had at least heard of them.

Part of the reason you haven’t heard of them is that they are in Taiwan (in Hsinchu)… Read More

Always-on Context-aware Sensors in Your Phone

Smartphones are smart but they are about to get smarter. The next big thing in mobile phones is to have a rich sensor environment: proximity, temperature and humidity, atmospheric pressure, light color, cover, gyroscope, magnetometer, accelerometer, ambient light, gesture and more. Some of these are already here, of course,… Read More

ST Endorses PowerArtist with ARM Cores & FDSOI libs

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

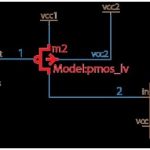

Designing Power Management ICs

With all the focus in design on SoCs in the latest sexy process (Hi-K Metal Gate! FinFETs!) it is easy to forget all the other chips that go into a system. When we say “system on a chip” there are actually very few systems that really get everything onto a single chip. One of the big areas that usually cannot go on the latest… Read More