Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Tag: power

OTP Memory to Build Smarter Power Management

All chips have critical power management requirements, often with multiple supply voltages. Digital power management ICs (PMICs) are commonplace to convert unregulated voltages from batteries and noisy power supplies to fully regulated accurate power to keep even the most sensitive chips performing.

Powervation is a company… Read More

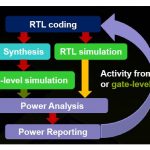

Efficient Power Analysis and Reduction at RTL Level

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

Qualcomm Video Friday

Two videos (both short) from Qualcomm. They are both amusing but also have a serious aspect to them. The first one is interesting since it is Qualcomm following in Intel’s footsteps with its “Intel Inside” campaign against AMD to make people care about what processor was in their PC. Until that point probably… Read More

Today’s Program is Brought To You by the Letter A

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

Analysis of Power, Thermal, EM, IR at DAC

Most EDA start-up companies have a narrow product focus to complement existing tool flows, however Invarian is taking a much bolder approach by offering tools for:

- Power analysis

- Thermal analysis

- EM / IR analysis

- 3D Thermal analysis

Atrenta: Mentor/Spyglass Power Signoff…and a Book

Today Atrenta and Mentor announced that they were collaborating to enable accurate, signoff quality power estimation at the RTL for entire SoCs. The idea is to facilitate RTL power estimation for designs of over 50M gates running actual software loads over hundreds of millions of cycles, resulting in simulation datasets in the… Read More

Interview with Forte CTO John Sanguinetti on Cynthesizer 5

Recently, Forte Design Systems announced the release of a new core engine to their popular high-level synthesis tool offering. It is a large undertaking, so I asked John Sanguinetti, Forte’s CTO, to answer some questions about that development effort.

Q. How long has it been since the last major upgrade of the Cynthesizer… Read More

Samsung’s Life of Pi @ Apache @ DAC

Last week I talked to Eileen You of Samsung-SSI to get a preview on what they will be talking about at Apache’s customer theater at DAC. Their presentation is titledThe Life of PI: SoC Power Integrity from Early Estimation to Design Sign-off. The ‘PI’ stands for Power Integrity.

Samsung-SSI’s operations… Read More

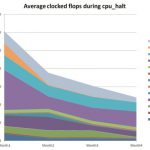

AMD Reduces Power by 20%

Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This… Read More