You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

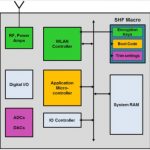

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP… Read More

Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one… Read More

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

All chips have critical power management requirements, often with multiple supply voltages. Digital power management ICs (PMICs) are commonplace to convert unregulated voltages from batteries and noisy power supplies to fully regulated accurate power to keep even the most sensitive chips performing.

Powervation is a company… Read More

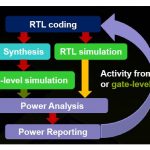

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

Qualcomm Video Fridayby Paul McLellan on 07-19-2013 at 11:30 amCategories: Arm, IP

Two videos (both short) from Qualcomm. They are both amusing but also have a serious aspect to them. The first one is interesting since it is Qualcomm following in Intel’s footsteps with its “Intel Inside” campaign against AMD to make people care about what processor was in their PC. Until that point probably… Read More

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

Most EDA start-up companies have a narrow product focus to complement existing tool flows, however Invarian is taking a much bolder approach by offering tools for:

- Power analysis

- Thermal analysis

- EM / IR analysis

- 3D Thermal analysis

…

Read More

Today Atrenta and Mentor announced that they were collaborating to enable accurate, signoff quality power estimation at the RTL for entire SoCs. The idea is to facilitate RTL power estimation for designs of over 50M gates running actual software loads over hundreds of millions of cycles, resulting in simulation datasets in the… Read More

Recently, Forte Design Systems announced the release of a new core engine to their popular high-level synthesis tool offering. It is a large undertaking, so I asked John Sanguinetti, Forte’s CTO, to answer some questions about that development effort.

Q. How long has it been since the last major upgrade of the Cynthesizer… Read More